Conforme aumenta la complejidad de las FPGAs y los ASICs modernos, los ingenieros empiezan a ser conscientes de que la verificación mediante simuladores HDL no es suficiente por sí misma para comprobar en su totalidad los requisitos de diseño a nivel del sistema de forma eficiente y ajustada a los plazos.

Muchos ingenieros actualmente emplean FPGAs para la aceleración y creación de prototipos de algoritmos. La utilización de FPGAs para procesar grandes cantidades de datos permite a los ingenieros evaluar rápidamente las compensaciones necesarias en los algoritmos y la arquitectura, así como comprobar los diseños en situaciones reales, evitando el peaje en tiempo que suponen los simuladores HDL. Las herramientas de diseño y comprobación a nivel del sistema como MATLAB y Simulink permiten a los ingenieros disfrutar de estas ventajas creando prototipos en FPGAs de sus algoritmos con rapidez.

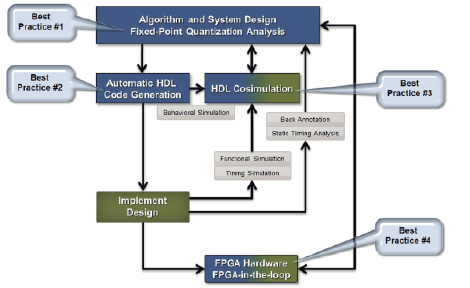

Este paper detalla las prácticas recomendadas para el diseño basado en modelos en relación con la creación de prototipos sobre FPGAs con MATLAB y Simulink. Las prácticas recomendadas se enumeran a continuación y aparecen destacadas en la Figura 1.

(1) Analizar el efecto de la cuantificación en punto fijo en una etapa temprana del proceso de diseño y optimizar la longitud de palabra con objeto de producir implementaciones de menor tamaño y mayor eficiencia energética.

(2) Utilizar la generación automática de código HDL para crear prototipos sobre FPGAs más rápidamente.

(3) Reutilizar los bancos de pruebas a nivel del sistema con cosimulación HDL para analizar las implementaciones HDL mediante métricas en el nivel del sistema.

(4) Acelerar la verificación con simulación FPGA-in-the-loop.

¿Por qué crear prototipos en FPGAs?

La creación de prototipos de los algoritmos en una FPGA aumenta la confianza en que tales algoritmos funcionarán en una situación real. Además de ejecutar vectores de pruebas y situaciones de simulación a gran velocidad, los ingenieros pueden usar prototipos en FPGAs para probar la funcionalidad del software y las funciones a nivel del sistema adyacentes, tales como los subsistemas analógicos y de RF.

Es más: dado que los prototipos en FPGAs se ejecutan con mayor rapidez, pueden utilizarse conjuntos de datos de mayor tamaño, que ofrecen la posibilidad de dejar al descubierto defectos que no detectaría un modelo de simulación.

El diseño basado en modelos mediante la generación de código HDL les permite a los equipos producir el primer prototipo antes que con un flujo de trabajo manual, tal y como se aprecia en la Figura 2.

Asimismo, este enfoque les ofrece a los ingenieros la posibilidad de realizar cambios en los algoritmos a nivel del sistema en lugar de a nivel de implementación, lo que acelera las iteraciones de hardware.

Caso práctico: conversor digital descendente

Con el fin de ilustrar las prácticas recomendadas para la creación de prototipos sobre FPGAs mediante el diseño basado en modelos, se empleará como caso práctico un conversor digital descendente (DDC). Un DDC es una pieza habitual de muchos sistemas de comunicaciones (véase la Figura 3).

Este elemento transforma una entrada de banda de paso de alta velocidad, que requiere considerables recursos computacionales para ser procesada, en una salida de banda base de baja velocidad, que puede ser procesada fácilmente con algoritmos DSP que precisan de menos potencia computacional.

Los principales componentes de un DDC son (véase la Figura 4):

– Oscilador controlado numéricamente (NCO)

– Mezclador

– Cadena de filtros digitales

Práctica recomendada nº 1: Analizar el efecto de la cuantificación en punto fijo en una etapa temprana del proceso de diseño

Los ingenieros suelen probar nuevas ideas y desarrollar los algoritmos iniciales mediante tipos de datos en punto flotante. No obstante, la implementación de hardware sobre FPGAs y ASICs requiere una conversión a tipos de datos en punto fijo, lo que suele provocar errores de cuantificación. En un flujo de trabajo manual, la cuantificación en punto fijo suele realizarse durante el proceso de codificación HDL. En este flujo de trabajo, el ingeniero no puede discernir fácilmente el efecto de la cuantificación en punto fijo comparando la representación en punto fijo con una referencia en punto flotante. Tampoco es fácil analizar la implementación HDL respecto de los desbordamientos.

Para tomar decisiones correctas sobre las longitudes de fracción necesarias, los ingenieros necesitan un modo de comparar los resultados de la simulación en punto flotante con los de la simulación en punto fijo antes de iniciar el proceso de codificación HDL. El incremento de la longitud de fracción reduce los errores de cuantificación; sin embargo, tal incremento no implica que haya que incrementar también la longitud de palabra (más superficie y más consumo de energía).

Por ejemplo, la Figura 5 ilustra las diferencias entre los resultados de la simulación en punto flotante y en punto fijo correspondientes a la fase 1 del filtro de paso bajo en la cadena de filtros del DDC. Estas diferencias se deben a la cuantificación en punto fijo. La figura de la parte superior muestra superpuestos los resultados de la simulación tanto en punto flotante como en punto fijo. La figura inferior muestra el error de cuantificación en cada punto del trazado. Según cuál sea la especificación de diseño, es posible que los ingenieros tengan que incrementar las longitudes fraccionarias para reducir el error de cuantificación introducido.

Además de seleccionar una longitud de fracción, los ingenieros deben optimizar la longitud de palabra para lograr diseños de bajo consumo y uso eficiente de la superficie. En el caso práctico del DDC, se utilizó Fixed-Point Designerpara reducir la longitud de palabra de algunas partes de la cadena de filtros digitales hasta en 8 bits (véase la Figura 6).

Práctica recomendada nº 2: Utilizar la creación automática de código HDL para producir prototipos en FPGAs más rápidamente

Se necesita código HDL para producir un prototipo en FPGA. Tradicionalmente, el código Verilog o VHDL se ha escrito a mano. Sin embargo, la alternativa de generar código HDL automáticamente mediante HDL Coder ofrece importantes ventajas. Los ingenieros pueden:

– Evaluar rápidamente si el algoritmo puede implementarse en el hardware.

– Evaluar rápidamente diferentes implementaciones de algoritmos y elegir la mejor.

– Crear prototipos de algoritmos en FPGAs con mayor rapidez.

En el caso práctico del DDC, generamos 5780 líneas de código HDL en 55 segundos. El código es legible y comprensible sin inconvenientes para los ingenieros (véase la Figura 7). La generación de código automático les permite a los ingenieros efectuar cambios en el modelo a nivel del sistema y producir una implementación HDL actualizada en cuestión de minutos mediante la regeneración del código HDL.

Práctica recomendada nº 3: Reutilizar los bancos de pruebas a nivel del sistema para la verificación de HDL con cosimulación HDL

La cosimulación HDL les permite a los ingenieros reutilizar modelos Simulink para enviar estímulos al simulador HDL y realizar análisis a nivel del sistema de la salida de simulación de forma interactiva (Figura 8).

Mientras que la simulación HDL proporciona tan solo salidas en forma de onda digital, la cosimulación HDL proporciona una visibilidad completa del código HDL, así como acceso a todo el conjunto de herramientas de análisis a nivel del sistema de Simulink.

Cuando se observa una diferencia entre los resultados previstos y los resultados de la simulación HDL, la cosimulación permite a los ingenieros entender mejor el efecto de la discrepancia a nivel del sistema.

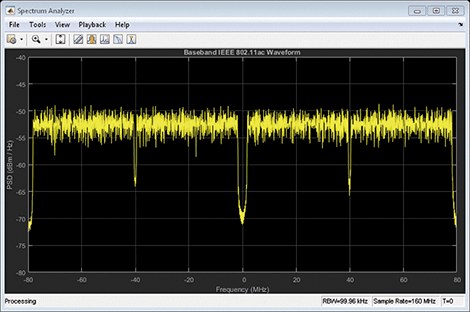

Por ejemplo, en la Figura 9 el visualizador del espectro permite al ingeniero tomar una decisión informada y hacer caso omiso de la discrepancia entre los resultados previstos y los de la simulación HDL, ya que las diferencias radican en la banda atenuada.

La salida de forma de onda digital, por contra, tan solo indica la discrepancia entre los resultados previstos y la simulación HDL como un error.

Si emplea tan solo la simulación HDL, el ingeniero podría llegar a la misma conclusión, pero tardaría más tiempo en llevar a cabo el análisis necesario.

Práctica recomendada nº 4: Acelerar la verificación con simulación FPGA-in-the-loop

Tras haber sido verificado mediante simulaciones HDL o cosimulaciones HDL, el algoritmo del DDC ya está listo para su despliegue en una placa de FPGA. La verificación basada en FPGAs (también conocida como “simulación FPGA-in-the-loop”) del algoritmo aumenta la confianza en que este funcionará en una situación real. Asimismo, les permite a los ingenieros ejecutar situaciones de prueba con mayor rapidez que con la simulación HDL tradicional.

En el caso del algoritmo del DDC, el modelo de Simulink se emplea para enviar estímulos de entrada a la FPGA y para analizar la salida de la FPGA (Figura 10). Al igual que ocurre con la cosimulación HDL, los resultados están disponibles en Simulink para su análisis.

La Tabla 1 compara los dos métodos de verificación (cosimulación HDL y simulación FPGA-in-the-loop) utilizados para el diseño del DDC.

En este caso, la simulación FPGA-in-the-loop fue 23 veces más rápida que la cosimulación HDL. Tales incrementos de velocidad permiten a los ingenieros ejecutar conjuntos de casos de prueba más amplios y realizar pruebas de regresión en sus diseños. Gracias a esto, pueden identificar áreas problemáticas en potencia que necesiten un análisis más detallado.

Aunque más lenta, la cosimulación HDL proporciona más visibilidad del código HDL. P

or tanto, es más conveniente para el análisis detallado de las áreas problemáticas que se detecten durante la simulación FPGA-in-the-loop.

Resumen

Siguiendo las cuatro prácticas recomendadas descritas en este artículo, los ingenieros pueden desarrollar prototipos en FPGAs con mucha más rapidez y con un mayor grado de confianza que utilizando el flujo de trabajo manual tradicional. Además, los ingenieros pueden seguir refinando sus modelos a lo largo del desarrollo y regenerar rápidamente el código para la implementación sobre FPGAs.

Esta capacidad posibilita que las iteraciones de diseño sean mucho más cortas que en un flujo de trabajo tradicional, que depende de código HDL escrito a mano.

Para obtener más información sobre el flujo de trabajo aquí descrito o descargar un kit técnico, visite:

http://www.mathworks.com/programs/techkits/techkit_asic_response.html.