Hay una demanda sin precedentes de tecnología que ayude a los diseñadores de sistemas de hoy en día a abrirse camino al mismo tiempo que la sociedad se conecta y comparte más dispositivos y datos a través de las redes. Mientras que los diseñadores de procesamiento de señales y comunicaciones trabajan para definir algoritmos que superen los retos urgentes en relación con el ancho de banda, la seguridad, la eficiencia energética, y la convivencia, hay una alarmante falta de diseñadores que creen soluciones eficaces de prototipos con señales del mundo real.

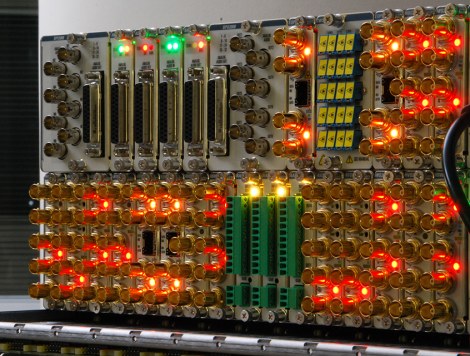

Mientras que la industria, el mundo académico y los laboratorios gubernamentales han recurrido a la radio definida por software (SDR) para evaluar los nuevos diseños con señales y condiciones del mundo real, el proceso de creación de prototipos está lejos de ser eficiente. Desafortunadamente, las herramientas de software existentes son a menudo un cuello de botella para la innovación; porque ofrecen un caudal de diseño indirecto e inconexo. El reto surge en gran parte de la discontinuidad entre unas herramientas bien adecuadas para el diseño del algoritmo y las necesarias para programar los componentes de hardware de SDR. Es precisamente esta discontinuidad la que puentea el paquete de software LabVIEW Communications System Design Suite, proporcionando un flujo de diseño unificado desde el algoritmo al hardware. Los diseñadores de hoy en día eligen SDRs porque la flexibilidad que ofrecen es una promesa para la creación rápida de prototipos. Esta flexibilidad surge principalmente de los elementos de computación que determinan el comportamiento de la entrada de RF genérica y del amplio ancho de banda de las SDRs modernas: los procesadores multinúcleo y las grandes FPGAs programables por el usuario. Desafortunadamente, las herramientas actuales para la programación de procesadores y FPGAs encuentran en las SDRs la erradicación de cualquier esperanza para la creación realmente rápida de prototipos. La transición del algoritmo a la implementación de un procesador y una FPGA exigen diferentes especializaciones y herramientas. Los equipos humanos de vanguardia en varios vectores tecnológicos son forzosamente mayores de lo ideal y se enfrentan a ciclos de diseño que son largos y costosos. El resultado no es un proceso de prototipado suave e iterativo que contribuya a la innovación; más bien, el proceso obstaculiza la eficiencia y frustra la innovación.

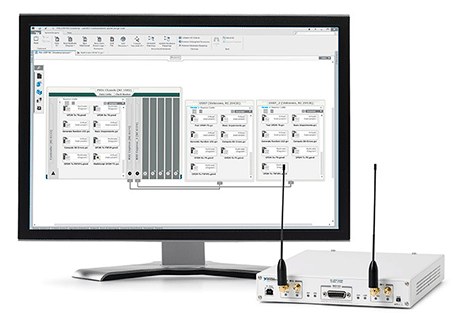

LabVIEW Communications ofrece un caudal de diseño unificado para la creación de prototipos de sistemas de comunicaciones. Se trata de un solo entorno de diseño coherente que puede actuar tanto sobre el procesador, como sobre la FPGA. Este entorno de diseño con reconocimiento de hardware incluye System Designer, que permite a los diseñadores validar la configuración del sistema, acceder a la documentación del mismo, describir su arquitectura, configurar sus componentes y particionar y desplegar algoritmos en el hardware. Esta incomparable integración de hardware-software proporciona acceso también a las E/S y a los recursos, eliminando la necesidad del middleware y del desarrollo de controladores.

Además, la avanzada tecnología de compilación que se encuentra en LabVIEW Communications permite una gran flexibilidad y facilita la descripción del algoritmo para dictar cómo estos algoritmos se mapean yejecutan en el hardware de SDRs. A modo de ejemplo para el desarrollo de algoritmos de procesamiento de señal, el nuevo diagrama de múltiples velocidades (MRD: Multi-Rate Diagram) incluido en LabVIEW Communications hace posible que los diseñadores se conecten a procesos que se ejecutan a un ritmo diferente sin el estorbo del protocolo, la utilización de memorias intermedias y la gestión de colas de datos entre procesos. Una vez que los investigadores diseñan la cadena de la señal en un diagrama de múltiples velocidades, pueden confiar en una herramienta integrada e interactiva basada en datos para convertir el diseño a coma fija y luego poder explorar cómo el diseño funcionaria bajo diferentes requisitos. La simple definición de la frecuencia del reloj y del rendimiento del algoritmo permite al compilador subyacente analizar la implementación y proporcionar a los diseñadores la temporización y la estimación de los recursos específicos del hardware de la SDR en el que desean realizar el despliegue. Los diseñadores están liberados de tener que lidiar con la arquitectura del hardware subyacente sobre el que quieren realizar el despliegue. Ya no tienen que diseccionar manualmente un diseño para comprender los compromisos entre las diferentes implementaciones. El compilador de LabVIEW Communications hace la a menudo compleja tarea de explorar el impacto del desenroscado de bucles, el particionamiento de la memoria, la modificación de los esquemas de acceso a memoria y la selección de los diferentes recursos de la FPGA y de los componentes. El diseñador puede avanzar gracias a la implementación que mejor se adapte a los requisitos del diseño en base a la retroalimentación del compilador. Como ventaja adicional, los investigadores puedan lograr una considerable reutilización, ya que los algoritmos básicos se definen en lenguajes de alto nivel y la implementación se deriva de los requisitos de diseño que se imponen al algoritmo.

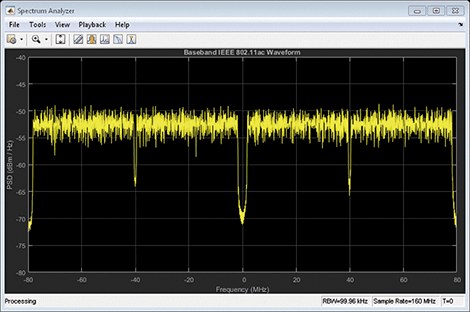

Por último, los usuarios pueden confiar en el nuevo Application Frameworks disponible en LabVIEW Communications para acelerar aún más su ciclo de diseño. Application Frameworks proporciona código fuente documentado, modificable y basado en estándares para LTE y 802.11 PHYs. Los diseñadores pueden centrar sus esfuerzos en los componentes específicos que están buscando para realizar mejoras sobre los diseños existentes de LTE y 802,11 en lugar de pasar el tiempo creando la infraestructura de requisitos necesaria para probar adecuadamente los nuevos algoritmos.

Los diseñadores de los sistemas de hoy requieren un flujo de diseño que perciba el verdadero potencial de las SDRs para la creación rápida de prototipos. LabVIEW Communications ofrece un camino sin problemas desde el algoritmo a la creación de prototipos, ayudando a los diseñadores a innovar más rápidamente. Los investigadores tienen acceso a lenguajes intuitivos de alto nivel que permiten el diseño de algoritmos eficientes y la simplificación del sistema. La naturaleza de reconocimiento de hardware por parte del software en el caso del hardware de las SDRs permite la integración precisa de las E/S del mundo real.

LabVIEW Communications ayudará a los diseñadores a superar a los competidores en la carrera para definir las normas que sirvan de base al 5G y a otros sistemas de comunicaciones futuras. Gracias a LabVIEW Communications, los diseñadores podrán percibir con mayor rapidez las soluciones que abren paso a la era de la “Internet de las Cosas”.