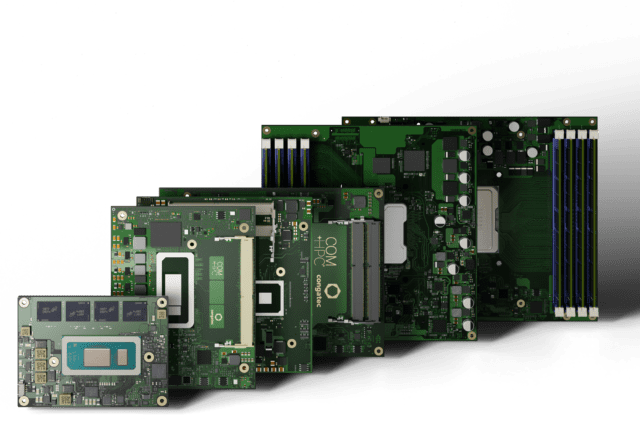

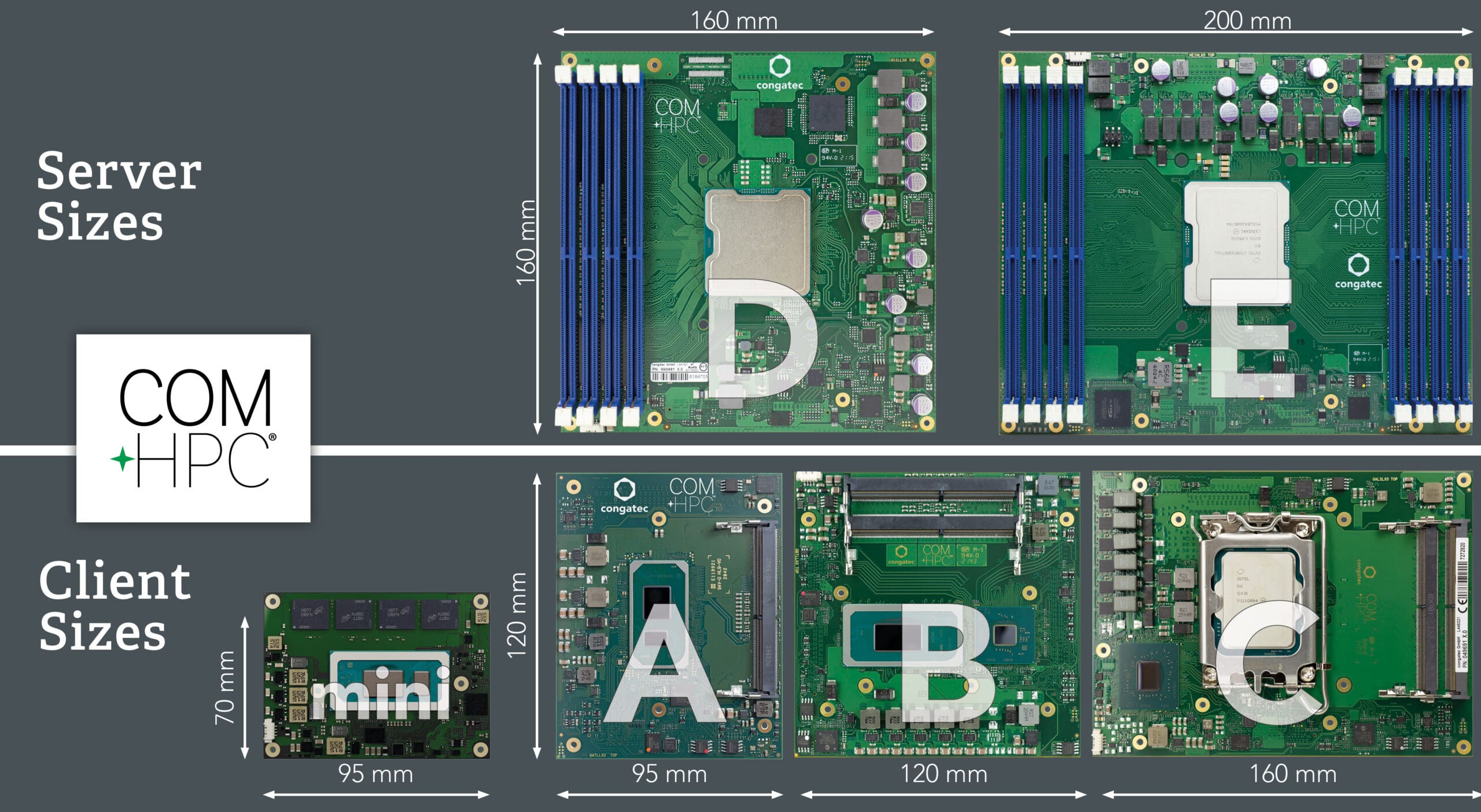

Figura 1. COM-HPC Mini es la incorporación más importante de la versión 1.2, que eleva el rendimiento de los clientes embebidos de gama alta a dispositivos móviles y fijos con limitaciones extremas de espacio.

La publicación Markt & Technik habla con Christian Eder, Presidente del grupo de trabajo COM-HPC y Director de Inteligencia de Mercado de congatec, sobre las principales innovaciones de este todavía joven estándar para módulos COM de altas prestaciones.

Sr. Eder, la especificación COM-HPC existe desde hace dos años y medio. ¿Cómo ha evolucionado la demanda en este tiempo?

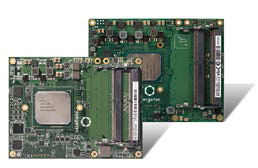

COM-HPC está diseñado para módulos COM (Computer-on-Modules) de alto rendimiento que pueden utilizarse como servidores modulares y como clientes modulares. Existe una gran demanda de este tipo de módulos debido a los crecientes requisitos de digitalización e IIoT, el uso de inteligencia artificial, la conciencia situacional basada en la visión y las necesidades de procesamiento de datos en espiral. Los desarrolladores que trabajan en nuevos diseños en estos campos de aplicación no tienen ninguna duda de que los módulos COM-HPC son la solución adecuada. Casi uno de cada dos nuevos proyectos dentro de toda la gama de prestaciones de los estándares PICMG, que incluyen COM Express y COM-HPC, utiliza COM-HPC, y ya se están produciendo en serie las primeras soluciones OEM con procesadores Intel Core de 12ª y 13ª generación e Intel Xeon D. Así pues, el lanzamiento de COM-HPC fue extremadamente sencillo y la aceptación fue alta desde el principio. La situación fue muy distinta cuando se lanzó la especificación COM Express. En aquel momento tuvimos que convencer mucho más. Sin duda, es una gran ventaja implicar a organismos independientes de los fabricantes, como el PICMG, en la especificación de nuevos factores de forma.

¿Qué pueden esperar los clientes de la nueva revisión?

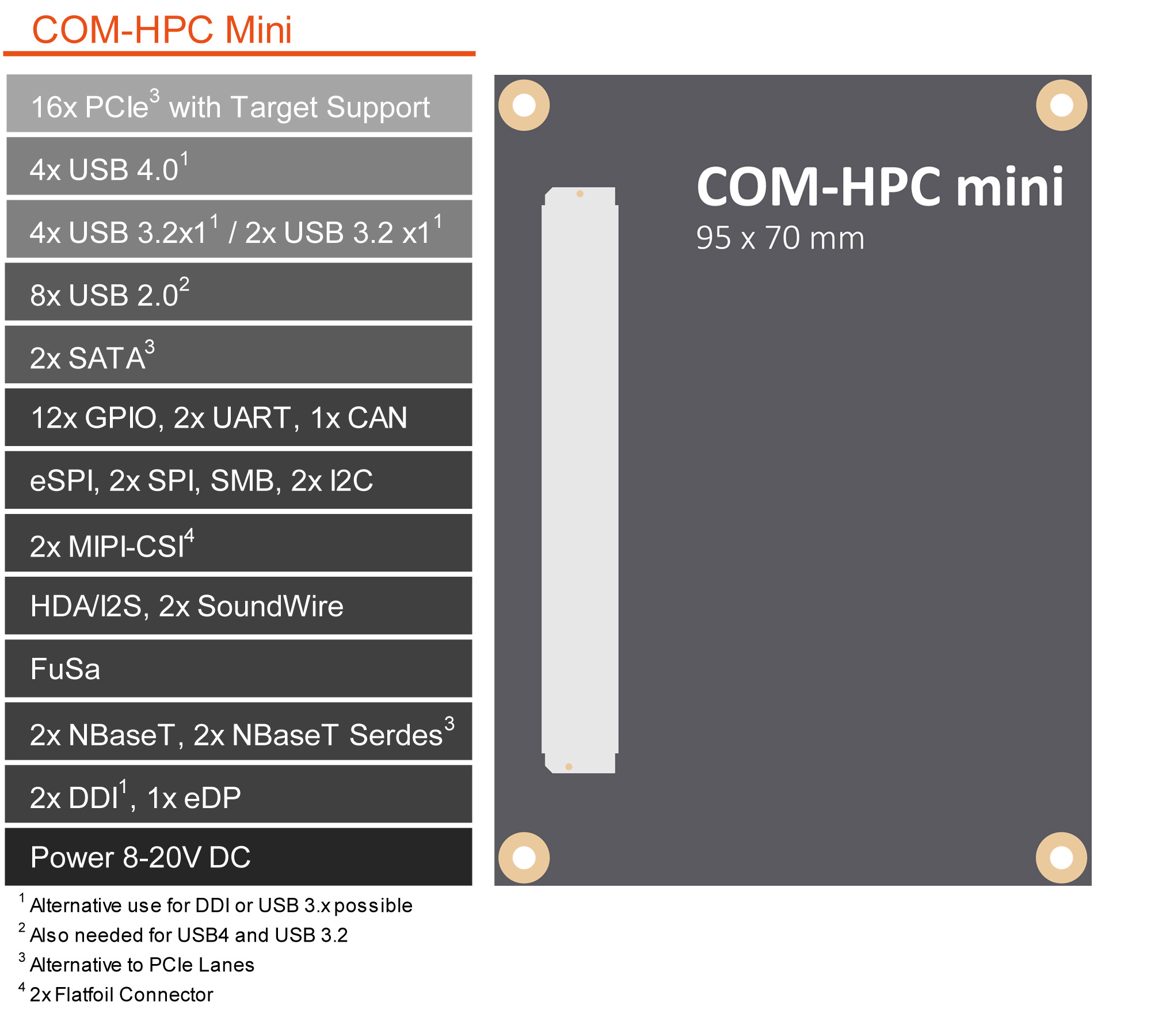

Hay algunas mejoras menores en las especificaciones que hacen que la norma sea aún más aplicable universalmente y mejoran la robustez de los diseños. Sin embargo, la innovación más importante es la incorporación de una nueva huella modular ultracompacta: COM-HPC Mini. Esta nueva especificación ofrece funciones de alto rendimiento en un formato especialmente pequeño de sólo 95 mm x 70 mm. Incluso los dispositivos con espacio limitado pueden beneficiarse ahora de la amplia interfaz de 400 pines y la oferta de mayor ancho de banda. Esto incluye Thunderbolt y PCIe Gen 5, así como Gen 6 en el futuro, una vez que estén disponibles los procesadores correspondientes.

COM-HPC se consolida así como el estándar para módulos COM más escalable que cubre una amplia gama de aplicaciones, desde diseños de pequeño factor de forma hasta servidores edge. Esto simplifica el proceso de diseño y facilita el desarrollo de completas familias de productos. Dado que los módulos COM-HPC no sólo admiten procesadores específicos como x86 o Arm, sino también FPGAs, ASICs y aceleradores de IA, proporcionan un estándar completo para el desarrollo de aplicaciones innovadoras basadas en las últimas tecnologías de sistemas embebidos y edge computing.

¿Por qué es tan importante la especificación Mini?

Por un lado, los dispositivos embebidos siempre tienen un espacio limitado, e incluso los más pequeños necesitan un enorme ancho de banda para la Inteligencia

Artificial y la conciencia situacional. Por otro lado, la huella de 95 mm x 70 mm es perfecta para la migración de COM Express a COM-HPC. En términos de requisitos de espacio, los módulos COM-HPC Mini encajan en cualquier diseño desarrollado sobre la base de COM Express Basic (95 mm x 120 mm) o Compact (95 mm x 95 mm). Esto facilita enormemente la migración, por lo que esperamos mucho de este factor de forma a largo plazo.

Pero, COM-HPC Mini tiene un 10% menos de pines que COM Express Type 6. ¿No limita eso las capacidades?

No. COM-HPC Mini está dirigido a dispositivos pequeños y móviles, no a sistemas estacionarios, a menudo muy complejos, con innumerables interfaces. Los desarrolladores que han explotado al máximo COM Express Type 6 son principalmente usuarios de COM Express Basic. Están migrando hacia COM-HPC Size A. Después de todo, no quieren perder la opción de ofrecer un número significativamente mayor de interfaces. Con 95 mm x 120 mm, este factor de forma también es ligeramente más pequeño que los 95 mm x 125 mm de COM Express Basic y ofrece una variedad y densidad de interfaces extremadamente altas. Sólo el hecho de que incorpore 800 pines en lugar de 440 proporciona más interfaces y ancho de banda. Es más, las interfaces rápidas como PCI Express o Ethernet son aún más rápidas en COM-HPC.

Teóricamente, el posible aumento del rendimiento de la interfaz de COM Express Type 7 (Rev. 3.0) a COM-HPC Server es de alrededor de un factor 15. De COM Express (Rev. 3.0) a COM HPC Client, el rendimiento de E/S puede incluso multiplicarse por 17.

Aparte del factor de forma y del conector de 400 pines, ¿existen otras diferencias entre COM HPC Mini y los demás factores de forma COM-HPC?

Sí, la asignación de pines es diferente. En algunos casos, incluye múltiples opciones para permitir la implementación de tantas configuraciones como sea posible con los 400 pines para ofrecer la máxima flexibilidad en la huella más pequeña. La asignación de voltaje de las señales de banda lateral también se ha adaptado para reducir los requisitos de alimentación y, lo que es aún más importante, para admitir procesadores de bajo consumo, que funcionan cada vez más a 1,8 voltios. Esto simplifica tanto el diseño del módulo como el de la placa base, ya que se necesitan menos convertidores de nivel en comparación con el mantenimiento de la misma especificación de los factores de forma COM-HPC de mayor tamaño. Por lo tanto, no es posible instalar módulos COM-HPC Mini en una placa base diseñada para el Size A porque los dos factores de forma son incompatibles, tanto eléctricamente como en términos de asignación de interfaces. El disipador térmico también es más plano para permitir diseños más finos. Además, la compatibilidad con MIPI-CSI no se realiza a través del conector de 400 patillas, sino a través de dos conectores planos adicionales de 22 patillas.

Así que, en efecto, la especificación COM-HPC Mini tiene 444 pines. Este enfoque de diseño con conectores adicionales se adoptó por analogía con SMARC y COM Express, donde ya ha demostrado su eficacia. En comparación con otros factores de forma mini, también hay otra cifra que destaca por qué COM-HPC Mini representa la gama alta absoluta: además del mayor número de pines, la compatibilidad con hasta 107 vatios deja reservas de energía significativamente mayores que los 15 vatios que suelen ser posibles con SMARC.

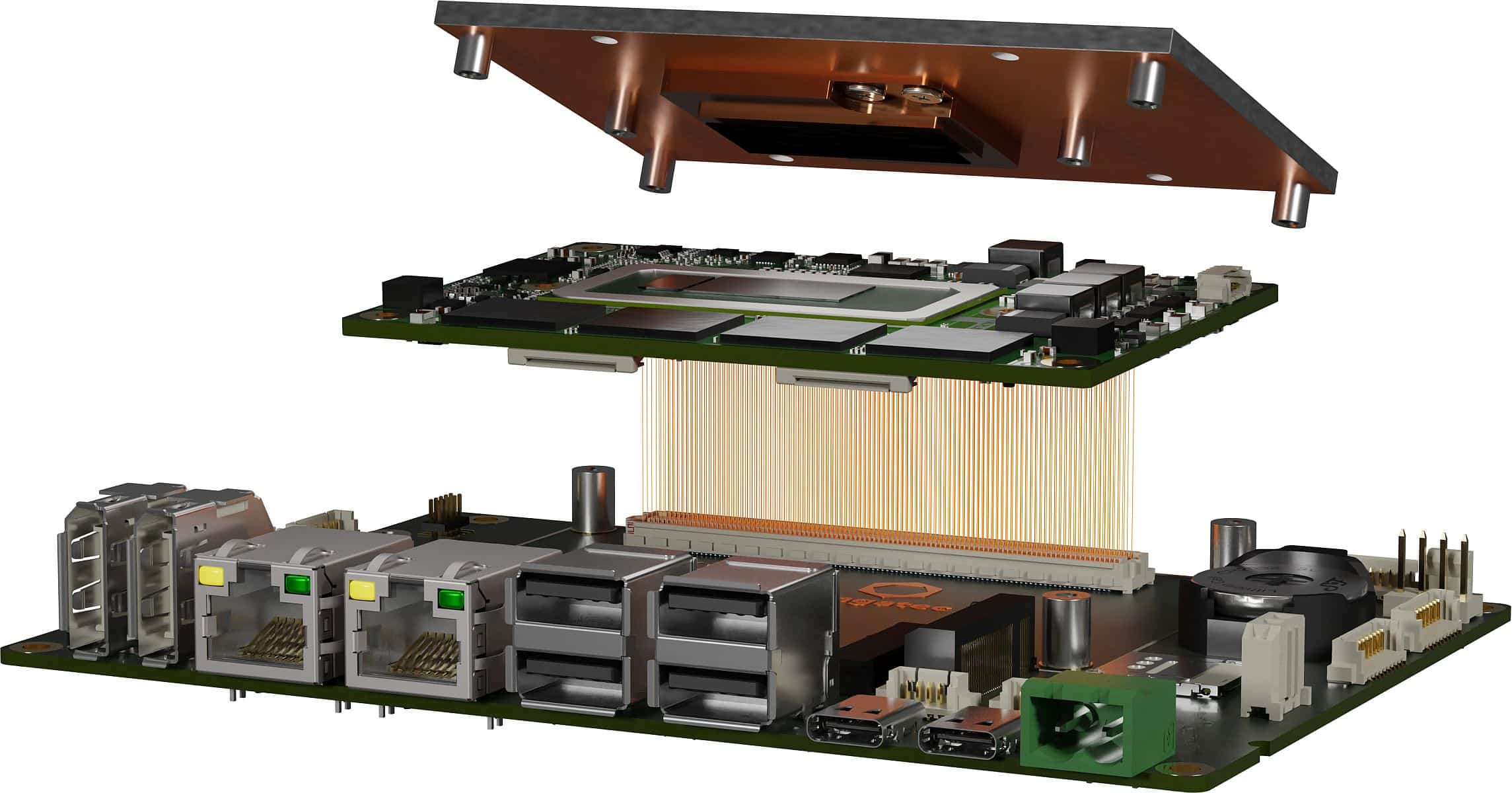

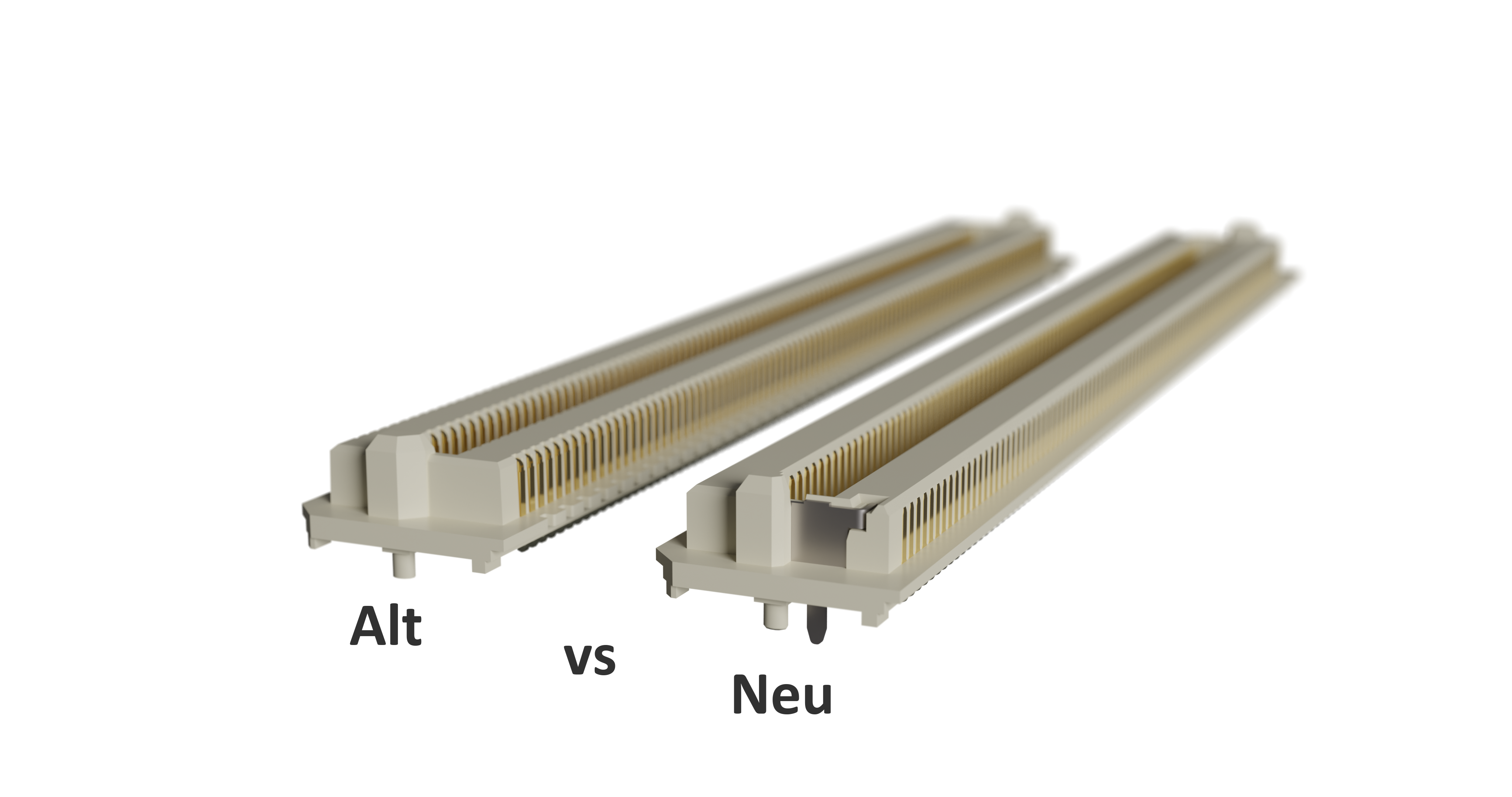

Figura 2. COM-HPC 1.2 especifica un nuevo conector para todos los tamaños de COM-HPC. Su clavija aumenta la estabilidad de la conexión entre placa y conector.

¿Podría explicarnos un poco la multiplexación? ¿No da lugar a configuraciones arbitrarias, que pueden dar lugar a incompatibilidades?

En comparación con COM-HPC Client, con su mayor número de pines, la especificación Mini ofrece 8 canales de datos de alta velocidad para las líneas de datos rápidas USB 3.x / USB 4 y para las interfaces de pantalla digital (DDI). Sin embargo, no todos los canales de datos pueden utilizarse para cualquier propósito. Por ello, hemos predefinido cinco opciones flexibles para escalar los 8 carriles SuperSpeed entre asignaciones DDI y USB. Además de 2x DDI y 4x USB3 por un lado y 4x USB4 por el otro, también son posibles variantes con 1x DDI, 1x USB4 y 4x USB3, así como 1xDDI, 2x USB4 y 2 USB3, y 3x USB4 y 2x USB2. Sin embargo, éstas son las únicas asignaciones permitidas, lo que ofrece seguridad de planificación. Lo mismo ocurre con la asignación de PCIe, Ethernet y SATA.

Los desarrolladores de Arm conocen desde hace tiempo el principio SERDES introducido con COM-HPC, que ha demostrado su eficacia. Sin embargo, para comprender el potencial de cada módulo individual, es necesario considerar el número significativamente mayor de combinaciones. Hasta cierto punto, SATA también es una concesión a los diseños heredados actuales. Sin embargo, esta opción apenas se utiliza ya que las numerosas interfaces PCIe también permiten el rápido almacenamiento masivo flash NVME.

Figura 3. El nuevo factor de forma Mini completa la especificación COM-HPC, convirtiéndola en el estándar COM más escalable del mercado.

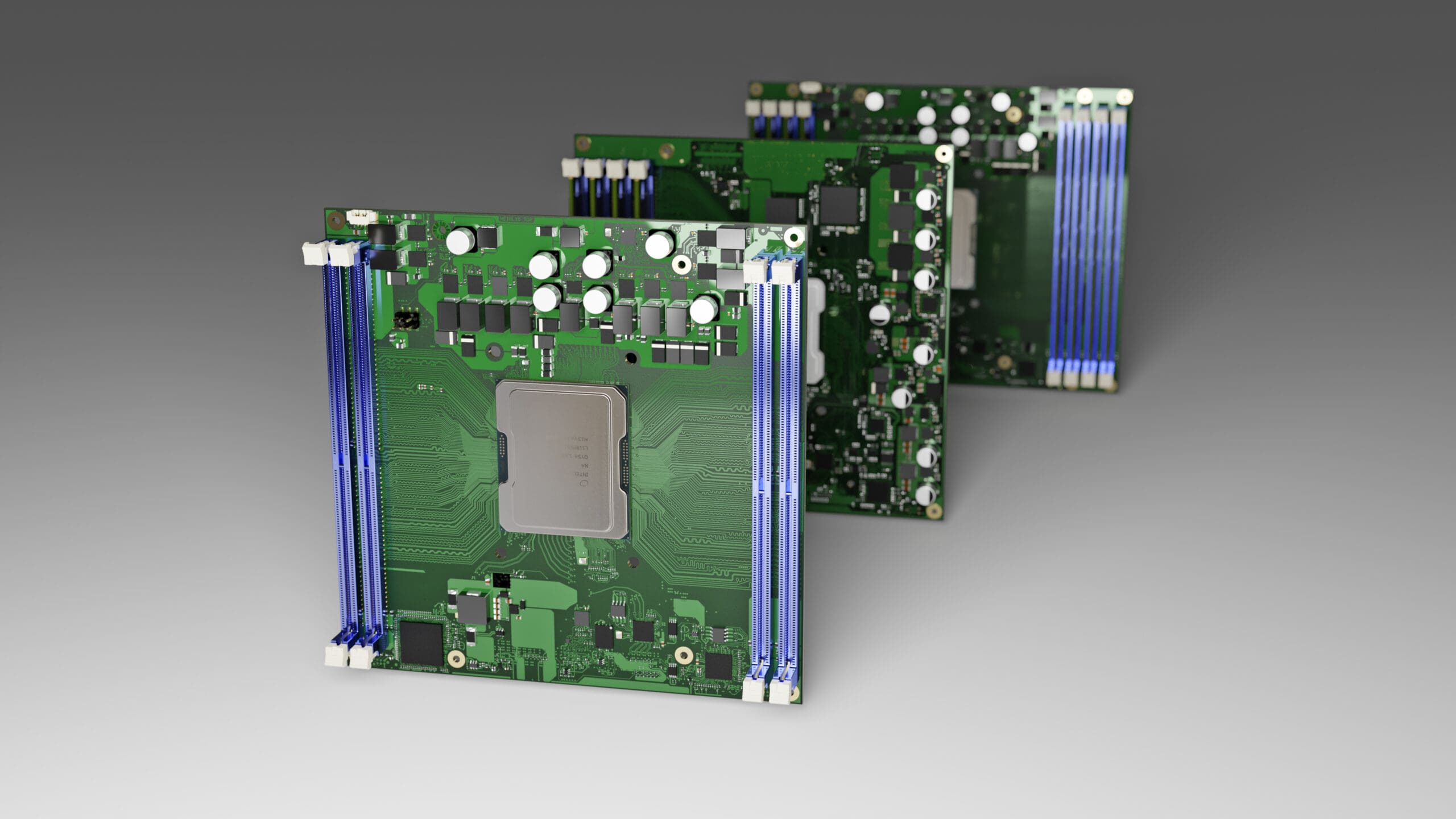

Echemos un vistazo a la cartera de servidores COM-HPC. ¿Qué está apareciendo aquí?

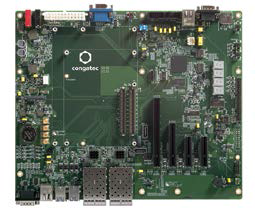

Cuando se lanzaron los procesadores Intel Xeon D, cuyo nombre en clave es Ice Lake D, fue interesante observar que los OEM no parecen necesitar todo el ancho de banda de memoria de estos procesadores. Esto significa que pueden confiar en el Size D, que ofrece sólo 4 en lugar de 8 ranuras para RAM. La razón de este fenómeno es que las aplicaciones de servidor edge crítico mixto no tienen que gestionar cargas de trabajo de servidor con uso intensivo de RAM. Más bien, deben alojar varias aplicaciones en tiempo real en paralelo y, por tanto, necesitan tantos núcleos como sea posible. También deben cumplir los requisitos de la comunicación industrial con muchos pequeños paquetes de mensajes que necesitan procesarse en tiempo real. También en este caso, el espacio de memoria no es tan crucial como en los servidores web con bases de datos que utilizan miles de personas simultáneamente.

Pasemos ahora a las nuevas características que se aplican a todos los factores de forma de la especificación. ¿Cuáles son los cambios más significativos?

Hay dos puntos a mencionar: En primer lugar, el conector se ha optimizado para aumentar aún más la robustez. En segundo lugar, COM-HPC está ahora totalmente cualificado para PCIe Gen 6.

Figura 4. COM-HPC Mini dispone de varias asignaciones de pines multiplexados, como SERDES para PCIe, GbE y SATA. Los 8 canales SuperSpeed también pueden tener diferentes interfaces DVI y USB.

¿El nuevo conector afecta también a la placa base?

Sí, se requieren dos pequeños orificios para aumentar la robustez. Y los refuerzos metálicos de los laterales del conector se sueldan para aumentar la estabilidad mecánica. Aparte de eso, no cambia nada. El nuevo conector reforzado sólo puede utilizarse si el segundo orificio también está presente. Sin embargo, tanto el conector antiguo como el nuevo pueden utilizarse con el mismo proceso de soldadura SMT. En este sentido, sólo es necesario un pequeño cambio en el diseño de la placa base para cumplir con la Rev. 1.2. Aunque preveo que el conector anterior seguirá estando disponible, tiene sentido evitarlo para los nuevos diseños de placas base. El cambio no plantea problemas: los conectores antiguos y nuevos pueden utilizarse en todas las combinaciones. Cabe destacar que el nuevo conector estará disponible en al menos tres fabricantes. Además de Samtec, Amphenol y All Best, ahora también se puede fabricar esta nueva variante bajo licencia, lo que permite estrategias de segunda fuente.

¿Qué cambios ha habido que introducir en los diseños de PCIe Gen 6? ¿Existen ya procesadores compatibles con este ancho de banda y quién necesita este rendimiento?

En general, ya es posible diseñar placas base para Gen 6 a pesar de que aún no existen procesadores compatibles con Gen 6. Sin embargo, estarán disponibles en un futuro no muy lejano. Para integrarlos, la placa base debe estar preparada para la modulación PAM4 en lugar de PAM2. Además de los valores 0 y 1, ésta utiliza dos etapas intermedias, con 2 en lugar de 1 bit por transmisión. Como esta actualización no cambia las frecuencias transmitidas, apenas se prevén nuevos retos para la integridad de la señal. Sin embargo, sigue siendo importante un diseño cuidadoso, ya que Gen 6 requiere una atención aún mayor al ruido de señal que Gen 5. El mayor ancho de banda de 8 GB/s por canal es necesario, por ejemplo, para los gráficos. Esto permite hasta 128 GB/s a través de 16 canales, lo que hace posible transmitir fotogramas de resolución cada vez mayor a frecuencias más rápidas y con mayor profundidad de color. 100 GbE ya es estándar en muchos ámbitos y este ancho de banda también debe transmitirse al procesador. USB también es cada vez más rápido.

¿Son posibles los diseños embebidos robustos con estos aumentos de rendimiento?

Afortunadamente, tenemos avances positivos en los procesos de fabricación hacia los 7 nm y más pequeños, así como en la tecnología 3D. Esto permite duplicar el rendimiento con el mismo TDP. Pronto lanzaremos nuevos procesadores con exactamente esta capacidad. Por tanto, podemos aumentar aún más el rendimiento manteniéndonos dentro de los límites de rendimiento con refrigeración pasiva. Esta es también la única forma de desarrollar sistemas embebidos que cumplan unos requisitos de sostenibilidad cada vez más exigentes, incluida la neutralidad climática.

Muchas gracias, Sr. Eder, por esta entrevista.

Figura 5. Al desplegar módulos de servidor COM-HPC, los fabricantes de equipos originales embebidos todavía tienden a utilizar el Size D con 4 ranuras de RAM. Esto se debe a que, normalmente, es necesario procesar muchos paquetes de datos pequeños en tiempo real en el extremo. Sin embargo, existen soluciones con 8 zócalos para necesidades de memoria mayores.