Autor: Steve Lou, especialista principal en marketing de productos

Hay dos aplicaciones principales para FemtoClock™ 3 Wireless (3W): una es para relojes de referencia SerDes PAM de 224 G, y la otra es inalámbrica para unidades de radio o celdas pequeñas “5G Advanced”.

Debido al aumento en los últimos tiempos de nodos de IA/granjas GPU, todas las velocidades de red están pasando de 112 G PAM4 a 224 G PAM4 SerDes (de 800 G a 1,6 T) para la IA de última generación. Varios proveedores de conmutadores Ethernet (Broadcom, Nvidia, Marvell y Cisco) tendrán soluciones de chipset de conmutadores Ethernet en el mercado en breve, y la solución de reloj de fluctuación ultrabaja se vuelve esencial para ellos. FemtoClock 3W (RC38312A) está destinado a esta aplicación.

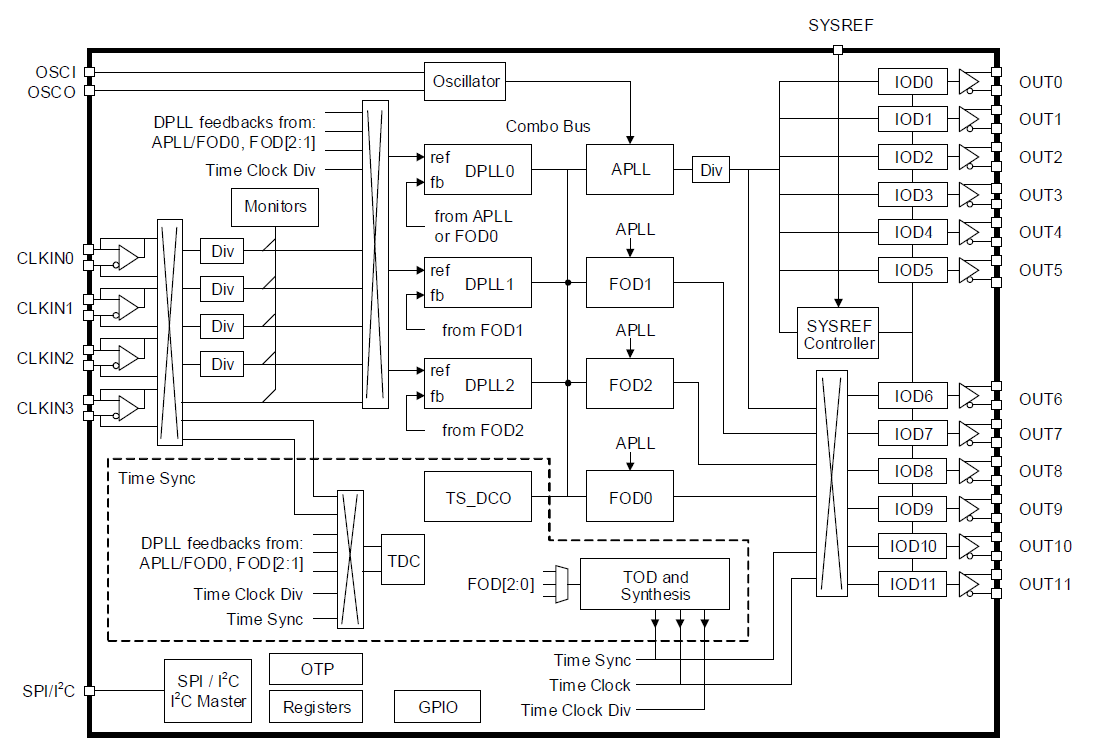

Figura 1. Diagrama de bloques de FemtoClock 3W (RC38312A)

El RC38312A cuenta con una impresionante gama de características diseñadas para aplicaciones de alto rendimiento. En su núcleo, incorpora un sintetizador de ruido de fase ultrabajo, que ofrece una fluctuación por debajo de 25 fs RMS, complementado con un filtro de paso alto de 4 MHz. El dispositivo está equipado con tres DPLL y tres FOD para admitir cuatro dominios de frecuencia distintos, lo que garantiza un funcionamiento versátil en diferentes sistemas.

Una característica destacada es su compatibilidad con los estándares JESD204B/C, lo que lo hace adecuado para una amplia gama de aplicaciones de alta velocidad.

También ofrece 12 salidas de reloj, cada una equipada con divisores de números enteros independientes. De estas salidas, 8 se pueden configurar como

LVDS, HCSL (AC-LVPECL) o CML, mientras que las 4 restantes admiten configuraciones LVDS, HCSL (AC-LVPECL) o LVCMOS.

El RC38312A admite un amplio rango de frecuencias de salida:

- Frecuencias CML desde CC hasta 2,5 GHz,

- Frecuencias LVDS o HCSL desde CC hasta 1 GHz,

- Frecuencias LVCMOS desde CC hasta 250 MHz.

Además, el dispositivo cuenta con cuatro entradas de reloj diferenciales u ocho de un solo extremo, lo que mejora aún más su versatilidad.

Al funcionar con una sola fuente de alimentación de 1,8 V, el RC38312A es energéticamente eficiente, ya que consume menos de 1,5 W, lo que lo convierte en una opción ideal para diseños que ahorran energía.

Requisitos de reloj para SerDes PAM4 de 224 G

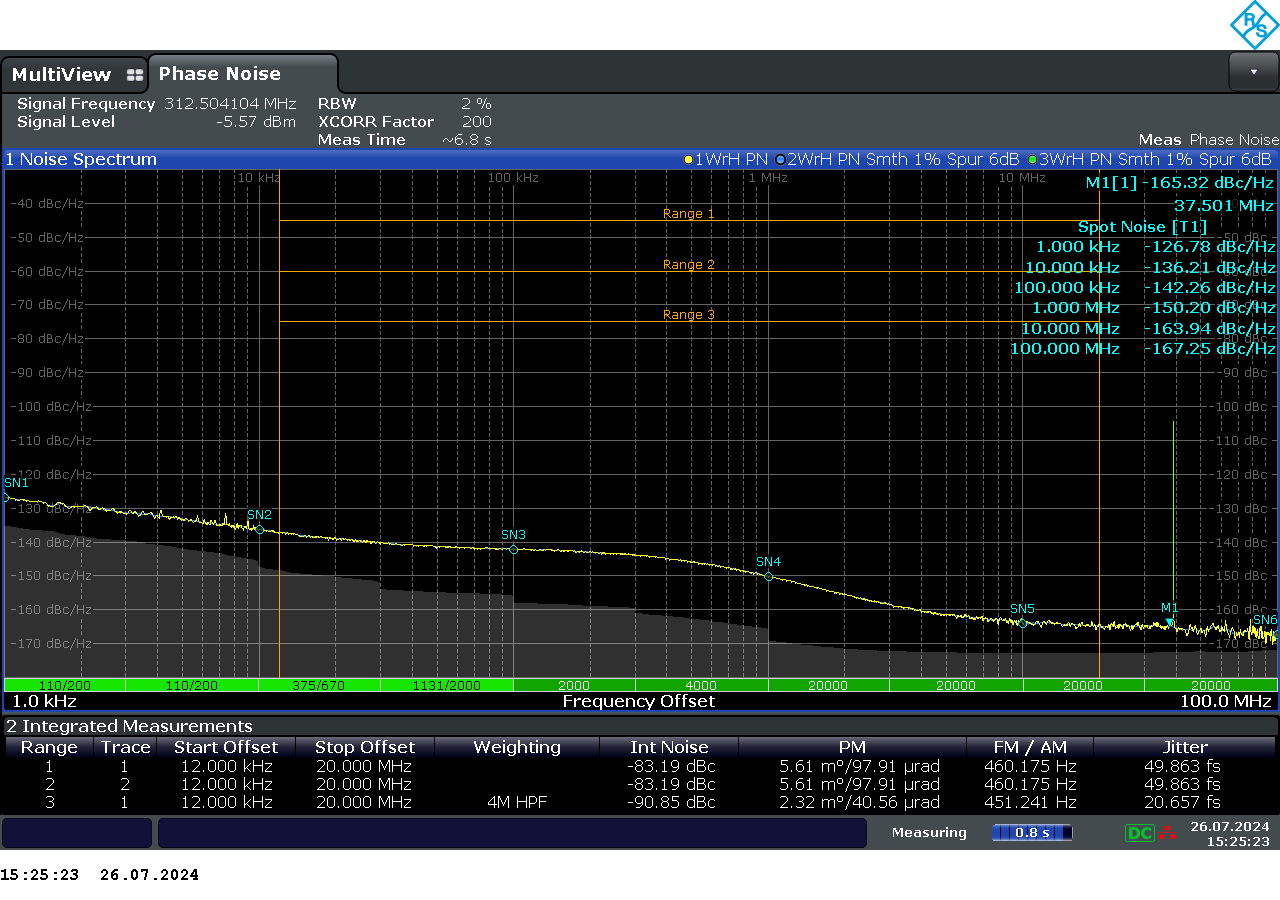

Los requisitos de reloj para SerDes PAM4 de 224 G son estrictos y FemtoClock 3 W puede cumplirlos. Los requisitos de fluctuación para PAM4 de 224 G están por debajo de 25 fs (12 kHz a 20 MHz) con HPF de 4 MHz y FemtoClock 3 W cumple con los requisitos dentro de un margen.

Figura 2. Diagrama que muestra un jitter ultrabajo de 20 fs

Compatibilidad con sincronización por cable e inalámbrica

Los sintetizadores de frecuencia de RF son componentes esenciales en el sistema de radio definido por software de comunicación moderno y avanzado. La pureza espectral de estos sintetizadores es fundamental, ya que afecta directamente la velocidad de datos máxima alcanzable y las características de potencia de ruido. En aplicaciones de RF, los sintetizadores deben ofrecer frecuencias altas con un amplio rango de sintonización y una resolución de frecuencia precisa. Lograr estos exigentes estándares de rendimiento requiere no solo un consumo de energía limitado y un área de chip compacta, sino también tonos espurios mínimos y ruido de fase.

En aplicaciones reales de 1024-QAM, puede comprender el impacto del jitter en el diagrama. El protocolo aún ayuda a reducir el error. En los sistemas de comunicaciones SDR comerciales, el mejor rendimiento del jitter del reloj es la estrategia clave para ganar el negocio para los clientes de primer nivel. Afecta la distancia de transmisión y la velocidad de datos.

Arquitectura avanzada

En el diseño de radio 4G, el sistema PLL utilizaba VCXO externo para proporcionar la solución de reloj de baja fluctuación y JESD204B/C fue diseñado por PLL y FPGA. La complejidad y el costo son los problemas clave para impulsar la innovación, y la sincronización estaba utilizando otro DPLL. Esto hace que el sistema de sincronización venga con Synch DPLL, FPGA y un atenuador de fluctuación de bucle doble con VCXO externo, 4 componentes en total.

En el diseño de radio moderno, FemtoClock 3W ha tenido mejoras que incluyen un solo chip que admite PLL de bajo ruido de fase, 3 DPLL, 3 FOD, bus combinado, motor SysREF/JESD204B/C y módulo TimeSync para la aplicación Sync.

Figura 3. Gráfico de ruido de fase de 122,88 MHz

Ruido de fase ultrabajo para aplicaciones de radio

Como se mencionó anteriormente, el ruido de fase es crítico para las aplicaciones de radio mmWave. FemtoClock 3W está diseñado en base al paquete BGA (baja diafonía), PLL de bajo ruido de fase (Kronos PLL), salida CML a 2,5 GHz (canal de salida de alta frecuencia), ajuste de fase y compensación.

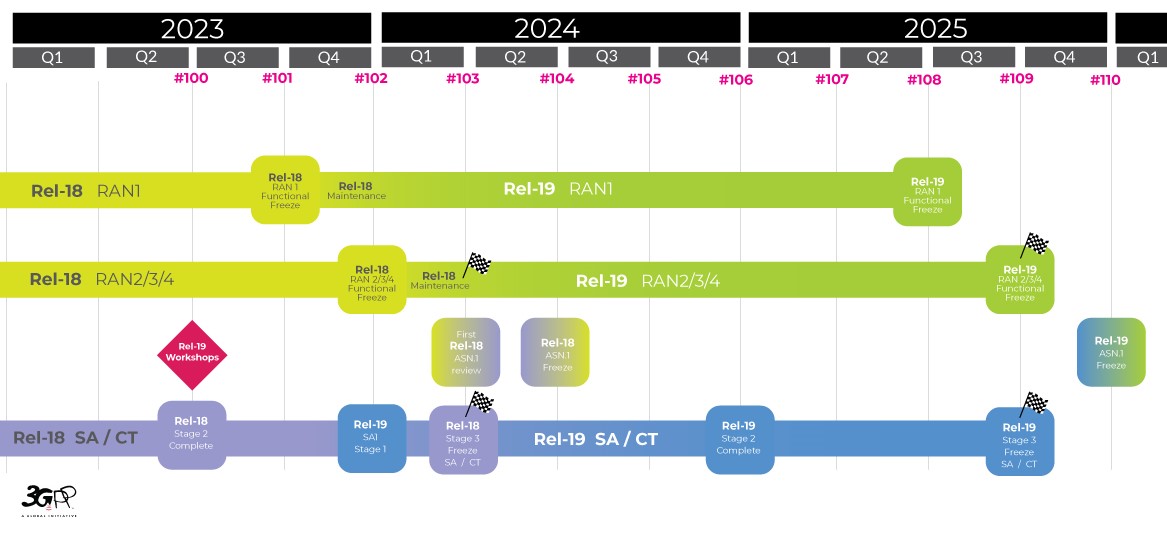

Cronograma 3GPP

El contenido de Rel-19 se decidió en los TSG de diciembre de 2023 (n.° 102) y es fundamental para los clientes que definen «5G-Advanced».

Conclusión

FemtoClock 3W es la última tecnología PLL de Renesas, compatible con aplicaciones inalámbricas y cableadas. Con una única fuente de alimentación de 1,8 V, ofrece el menor consumo de energía y una salida de reloj con fluctuación de fase ultrabaja.

FemtoClock 3W es la mejor solución de reloj tanto para unidades de radio inalámbricas como para relojes de referencia SerDes PAM4 de 224 G para conmutadores Ethernet de 1,6 T.

Para comenzar a evaluar FemtoClock 3W, ¡obtenga un kit de evaluación hoy mismo!

renesas

renesas