Autor: Graeme Clark, Ingeniero Principal, Renesas Electronics

Tradicionalmente, los sistemas de microcontroladores han utilizado dispositivos periféricos simples para expandir la funcionalidad del microcontrolador maestro, donde existe la necesidad de una función adicional no implementada en el dispositivo. Estos buses periféricos generalmente se han conectado mediante un bus en serie en la PCB al microcontrolador maestro. Los buses serie son una solución ideal para la expansión, ya que normalmente ocupan menos espacio en la placa de circuito impreso que una implementación de bus paralelo completo. También utilizan menos pines de E/S en el microcontrolador, al mismo tiempo que ofrecen velocidades de datos lo suficientemente altas para la mayoría de las aplicaciones y consumen menos energía que una implementación de bus paralelo.

Estos dispositivos en serie suelen ser físicamente pequeños, usan paquetes compactos de 8 o 16 pines y, a menudo, tienen un coste muy bajo. Hay disponible una amplia gama de funciones, desde dispositivos de memoria simples, como EEPROM serie y SRAM, hasta dispositivos complejos como convertidores analógicos a digitales avanzados.

El advenimiento de dispositivos más complejos, especialmente dispositivos móviles como teléfonos móviles y dispositivos portátiles, ha dado una nueva vida a estos buses serie, lo que permite la conexión de una amplia variedad de sensores complejos a la CPU maestra mientras se minimiza el espacio de la placa de circuito impreso.

Un tipo común de bus serie que se utiliza para la expansión de periféricos en muchos sistemas es la Interfaz de periféricos serie (SPI), desarrollada por primera vez por Motorola en la década de 1980. Esto se ha convertido casi en un estándar de facto para muchos usuarios. Inicialmente, fue especialmente popular entre aquellos que querían agregar pequeñas memorias no volátiles a su sistema, pero con el tiempo, la cantidad de dispositivos compatibles con SPI ha crecido para ofrecer una amplia gama de funciones diferentes.

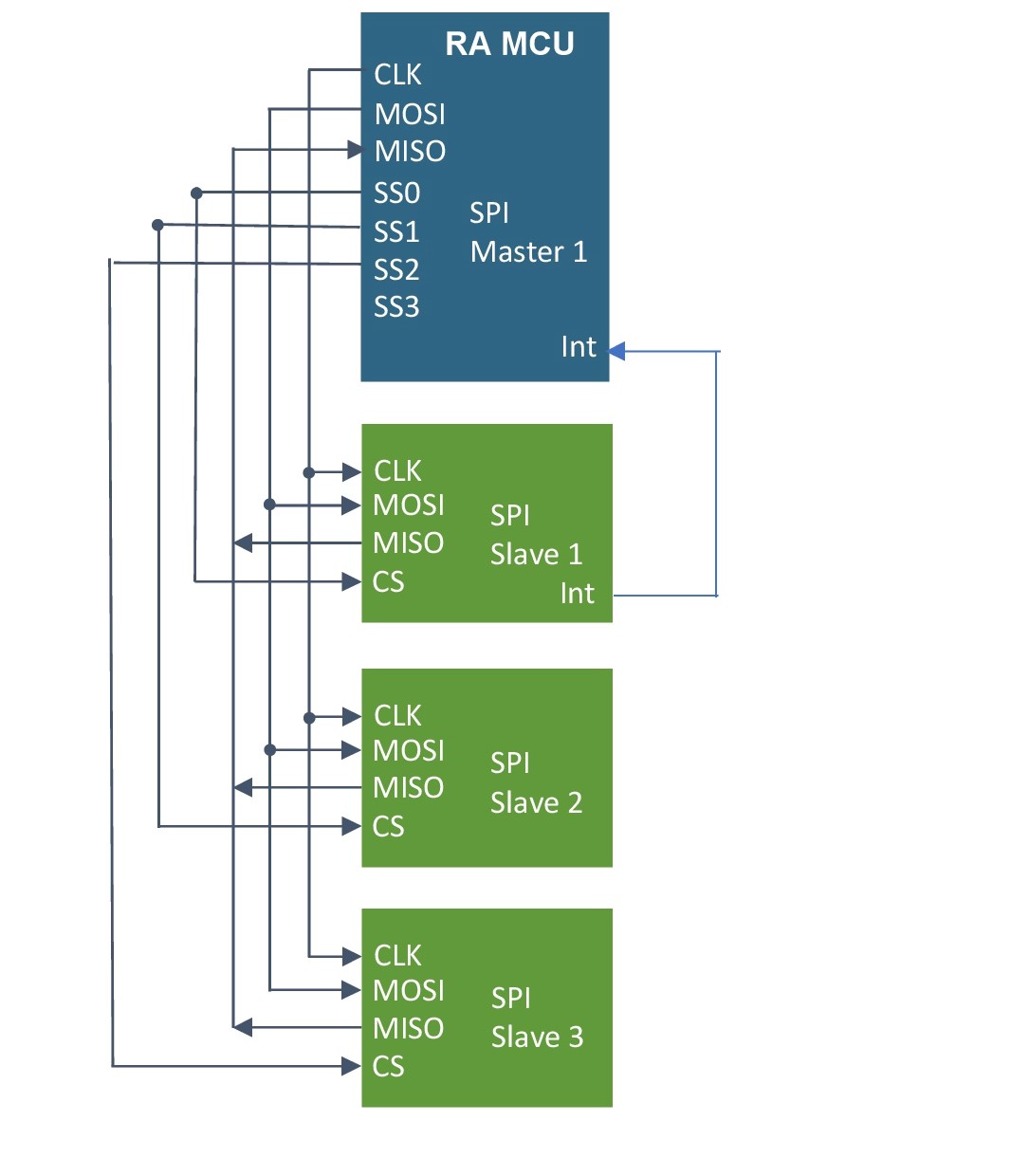

El bus SPI es un bus de 4 hilos que se puede considerar como un búfer circular, ya que los datos se transfieren tanto del maestro como del esclavo al mismo tiempo y se sincronizan mediante una señal de reloj, mientras que los dispositivos individuales se seleccionan mediante un pin adicional. . La Figura 1 muestra un sistema SPI típico.

Figura 1. Sistema SPI típico

El bus SPI, normalmente tiene un único bus maestro que gestiona todas las transferencias de bus. Son posibles múltiples maestros de bus, pero esto aumenta significativamente la complejidad del sistema.

El bus consta de al menos 4 señales:

- CLK: reloj serie que sale del maestro

- MOSI: Master Out Slave In donde los datos se envían desde el maestro

- MISO: Master In Slave Out donde los datos se envían desde un dispositivo esclavo

- CS/SS: Selección de chip o esclavo que sale del maestro que se usa para seleccionar un dispositivo esclavo en particular y para indicar que se están enviando datos

Si bien SPI puede usar muchos pines para en el bus, es capaz de operar a altas velocidades, y algunos dispositivos admiten velocidades de transferencia de hasta 60 MHz o más. Recientemente, la especificación ha crecido aún más en términos de la cantidad de líneas de datos, con el bus Quad SPI (QSPI) convirtiéndose en un periférico común. Ofrece características avanzadas como “Execute in Place” (XiP) permitiendo que las aplicaciones se ejecuten directamente desde la memoria serie y obtengan datos a velocidades extremadamente altas.

SPI tiene varias ventajas, incluido el soporte para comunicaciones dúplex completas, alta velocidad y un mecanismo de comunicaciones simple que requiere un controlador de software simple y fácil de desarrollar. En el diagrama de bloques de una aplicación SPI típica en la Figura 1, está claro que se utilizan muchos pines de E/S para admitir la transferencia de datos en serie, especialmente cuando se utilizan varios periféricos.

SPI también ha desarrollado varios «tipos» diferentes a lo largo de los años y esto puede complicar la elección de periféricos específicos, con variaciones del reloj y su polaridad.

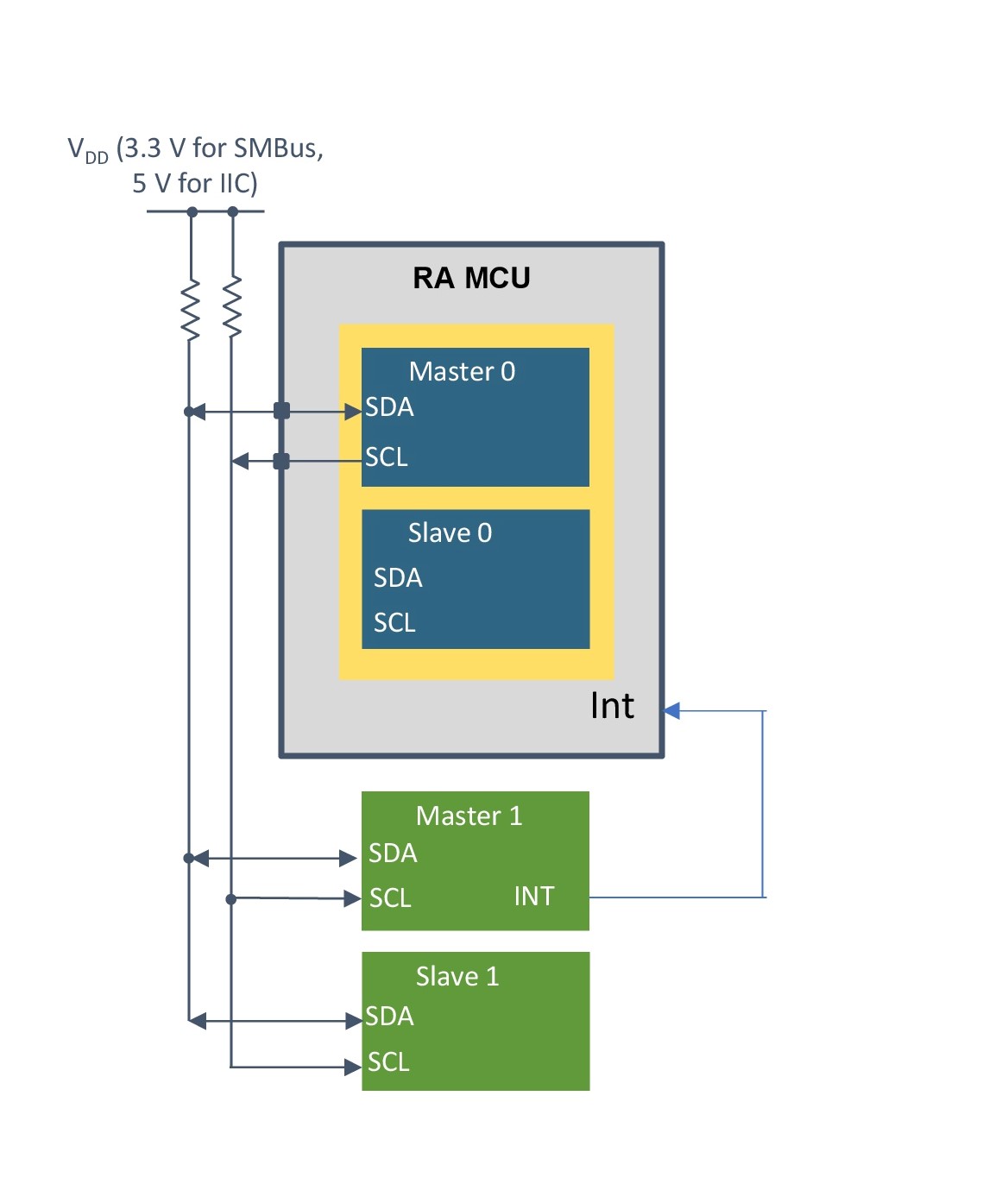

Otro bus serie popular es el Inter “Integrated Circuit” o I2C Bus, desarrollado por primera vez por Philips en la década de 1980. El bus I2C utiliza dos señales bidireccionales de open-drain, la línea de datos en serie (SDA) y la línea de reloj en serie (SCL) para transmitir reloj y datos. Cada línea de señal está conectada a una resistencia pull-up.

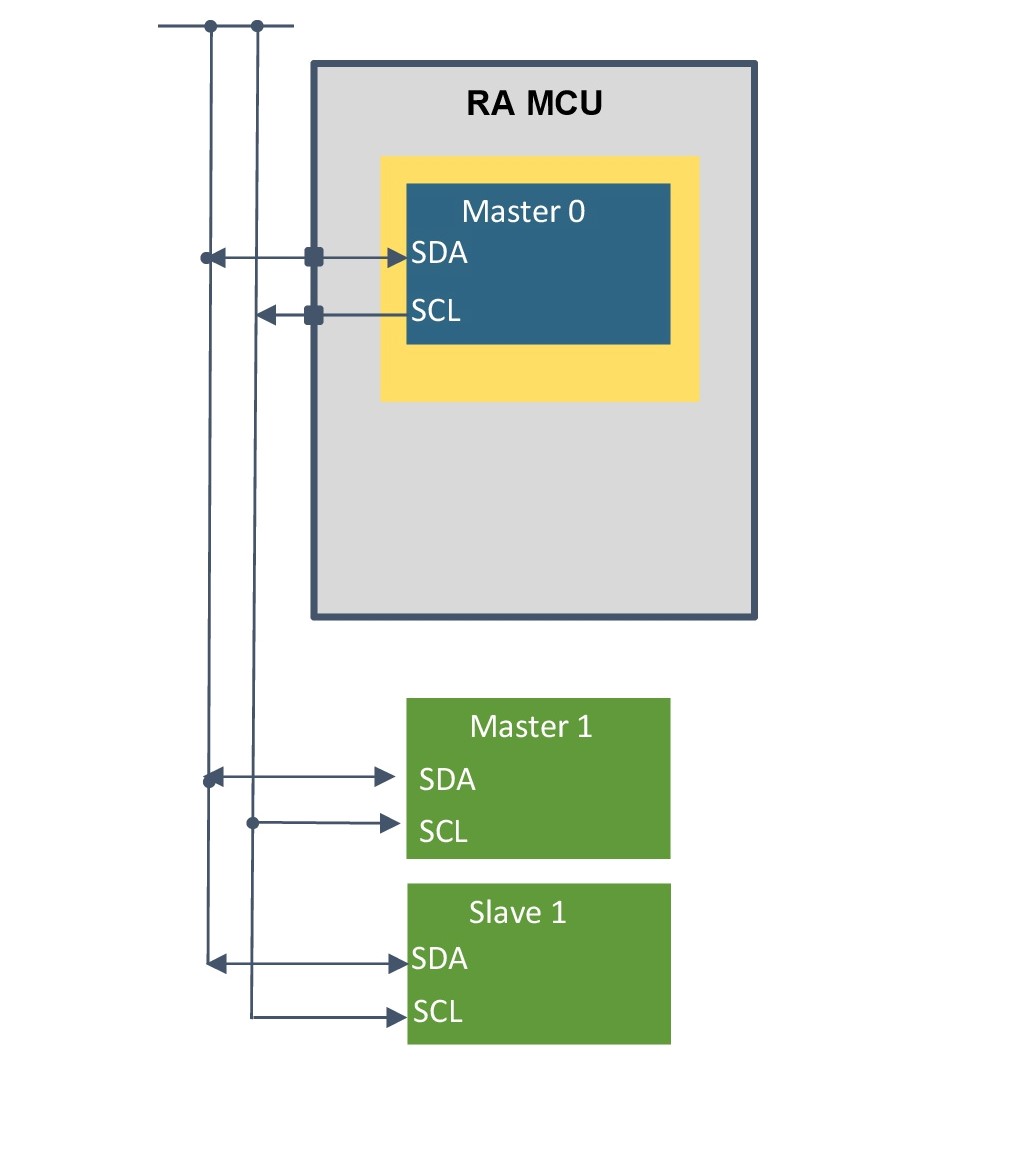

I2C admite un protocolo en el que se codifica en el mensaje una dirección de 7 bits del dispositivo esclavo e información de registro adicional. Debido a la configuración del bus con el uso de salidas open-drain, se puede soportar fácilmente la operación multimaestro. I2C ha sufrido una serie de revisiones a lo largo de los años. Las versiones iniciales solo admitían velocidades de datos de hasta 100 kbps, y las versiones más nuevas admiten velocidades de datos más altas: hasta 3,4 Mbps en modo de alta velocidad, así como funciones adicionales como el direccionamiento de 10 bits. La Figura 2 ilustra una configuración de bus I2C típica.

El bus I2C se ha revisado varias veces desde su lanzamiento inicial. Ahora puede admitir velocidades de transferencia de datos de hasta 5 Mbps. El uso de un protocolo más complejo permite a los usuarios crear sistemas más complejos con múltiples maestros de bus usando solo dos pines, sin embargo, los controladores de software para dispositivos I2C tienden a ser más complejos.

Figura 2. Ejemplo de I2C típico

Otra gran desventaja de los buses SPI e I2C es que ninguno tiene forma de implementar interrupciones dentro de sus estructuras de bus, por lo que, si sus periféricos serie necesitan generar interrupciones, debe conectarlos a pines adicionales en su microcontrolador, nuevamente puede vea el uso de un pin externo en las Figuras 1 y 2.

A medida que los sistemas se vuelven más complejos y necesitamos conectarnos a muchos más dispositivos serie con más datos y velocidades más altas, los sistemas que utilizan implementaciones tradicionales de SPI e I2C han comenzado a tener problemas. El requisito de encontrar una nueva solución fue impulsado por las necesidades de las aplicaciones móviles de baja potencia, mientras se buscaba mantener cierta compatibilidad básica con versiones anteriores de los buses existentes.

La interfaz I3C (oficialmente el «Circuito inter integrado mejorado de la Alianza MIPI») fue desarrollada originalmente por la alianza MIPI para admitir la interconexión de sensores en aplicaciones móviles. La alianza MIPI es una alianza global de empresas de electrónica que desarrollan especificaciones técnicas para aplicaciones móviles. Renesas Electronics es miembro de esta.

El concepto original detrás de la interfaz I3C era estandarizar la comunicación entre los sensores y la CPU host, para reducir la cantidad de pines físicos y la interconexión, así como para admitir comunicaciones de alta velocidad y bajo consumo. El I3C fue diseñado para reemplazar los buses I2C y SPI que se usan normalmente hoy en día en estas aplicaciones y para mejorar la especificación. Si bien el objetivo inicial eran los dispositivos móviles, pronto se hizo evidente que los mismos requisitos son adecuados para muchas otras aplicaciones que incluyen buses serie simples que brindan interconexión local entre dispositivos.

La interfaz I3C resuelve algunos de los problemas que tenemos con los buses I2C y SPI existentes. Los beneficios que ofrece la interfaz I3C incluyen:

- Compatibilidad con velocidades de datos más altas

- Las interrupciones en banda eliminan la necesidad de pines adicionales para admitir selecciones de chip (SPI) o interrupciones.

- Compatibilidad con direcciones dinámicas

- Compatibilidad con conexión en caliente

- Compatibilidad con comandos en banda

- Compatibilidad con muchos dispositivos I2C heredados

- Bajo consumo de energía

Figura 3: Operación I3C

La interfaz I3C puede operar en una variedad de modos diferentes que ofrecen varias velocidades de datos.

- Velocidad de datos estándar (SDR): admite hasta 12,5 Mbps

- Alta velocidad de datos: doble velocidad de datos (HDR-DDR): admite hasta 25 Mbps

- High Data Rate-Tertiary Symbol Pure (HDR-TSP): admite hasta 33,3 Mbps

- High Data Rate-Tertiary Symbol Legacy (HDR-TSL): admite hasta 33,3 Mbps

Cada uno de estos modos ofrece importantes ventajas de rendimiento sobre el bus I2C. Sin embargo, la velocidad de datos real lograda en una aplicación real será menor debido a las funciones adicionales presentes en el protocolo. Los modos HDR usan SDR y los modos HDR-TSL admiten periféricos I3C y dispositivos I2C heredados en el mismo bus. Cabe señalar que los modos de alta velocidad de datos no están disponibles en la especificación básica I3C.

La comunicación se inicia en modo SDR y se puede emitir un comando de bus para cambiar al modo HDR para acceder a dispositivos capaces de operar en este modo. La capacidad de enviar comandos como parte de la estructura de paquetes I3C también abre muchas más posibilidades para controlar dispositivos sensores. La especificación I3C define tanto los códigos de comando comunes como la capacidad de crear sus propios códigos de comando definidos por el usuario.

I3C ofrece compatibilidad con versiones anteriores del bus I2C, lo que permite que se admitan dispositivos y aplicaciones heredados, pero existen algunas limitaciones que deben administrarse. Estos incluyen el cambio open-drain (I2C) a push-pull (I3C) para el reloj y las líneas de datos, y la falta de soporte para la expansión del reloj, que a veces se usa para permitir que algunos dispositivos I2C respondan a una solicitud de datos.

La función de interrupción en banda admitida por I3C es particularmente importante, ya que se puede usar como una función de reactivación de bajo costo y al mismo tiempo permite que los dispositivos ingresen en un modo de apagado de bajo consumo al mismo tiempo que respaldan la operación correcta en el bus. Los usuarios no necesitan usar los pines adicionales asociados con las interrupciones en los otros buses.

I3C también puede ahorrar una cantidad considerable de energía del dispositivo a través de velocidades de datos más altas (porque el dispositivo se puede volver a dormir antes), configuración y control integrados (sin entrometerse en los principales protocolos de comunicación), Interrupción en banda (IBI) como un bajo -Mecanismo de reactivación de costo y la capacidad de los objetivos para apagar todos los relojes internos sin dejar de funcionar correctamente en la interfaz I3C.

I3C también puede ahorrar energía en comparación con la utilizada por I2C, ya que la energía consumida por transferencia de bits es más eficiente que la que se logra con el bus I2C. Esto se debe al uso de push-pull (frente a open-drain) y una fuerte señalización pull-up.

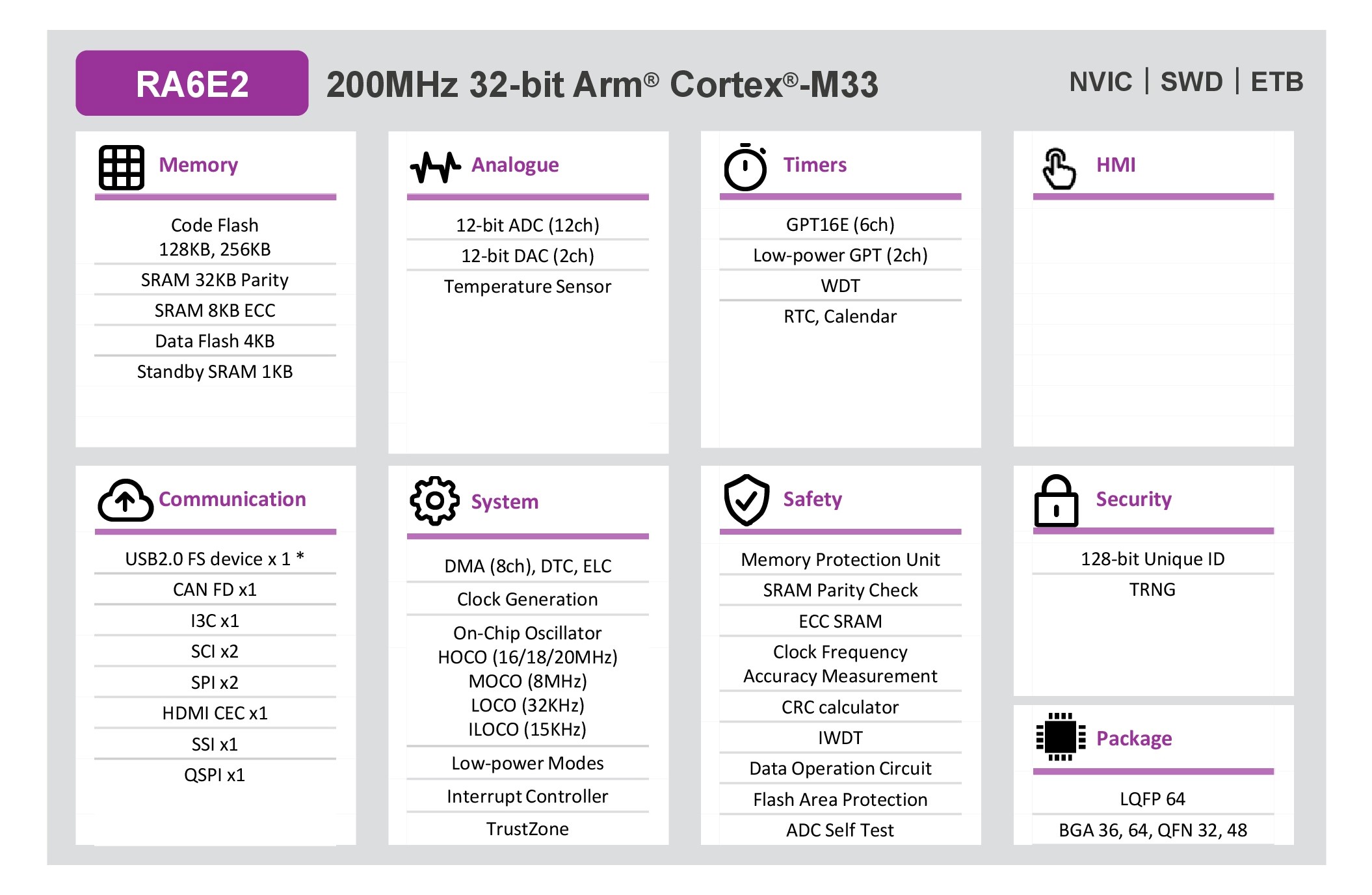

Renesas ha desarrollado dos nuevas familias de microcontroladores basadas en el núcleo Cortex M33 de Arm, el RA4E2 de 100 MHz y el RA6E2 de 200 MHz. Estos dispositivos se han diseñado para proporcionar una solución ideal para productos que necesitan recopilar datos de una gran cantidad de sensores. Cada dispositivo incluye una interfaz I3C, así como múltiples interfaces I2C y SPI combinadas en paquetes tan pequeños como QFN de 32 pines o BGA de 4 x 4 mm. Estos dispositivos ofrecen niveles de rendimiento significativos, lo que permite el uso de algoritmos de software complejos para administrar los datos de múltiples sensores y procesar los datos del sensor en el dispositivo, minimizando la necesidad de compartir datos detallados con un procesador host.

La combinación de estos dispositivos, con varios sensores seriales conectados por el bus I3C, permite crear sistemas de sensores compactos y de bajo consumo. La Figura 4 muestra un diagrama de bloques del RA6E2 de 200 MHz.

Figura 4. Diagrama de bloques del RA6E2.

La especificación completa de la especificación MIPI I3C solo está disponible para los miembros de la alianza MIPI. Sin embargo, la especificación básica MIPI I3C agrupa las funciones I3C más comunes y está disponible para su uso sin membresía MIPI, lo que permite a los usuarios usar la interfaz I3C en sus aplicaciones de interconexión.

La interfaz I3C proporciona una actualización integral de los buses I2C y SPI que se utilizan normalmente para conectar sensores y CPU host en muchas aplicaciones hoy en día, lo que facilita la transferencia de datos entre estos dispositivos y reduce el consumo de energía del sistema.

En la próxima generación de sensores inteligentes, muchos de los cuales tendrán requisitos de procesamiento local para minimizar la carga de la CPU del host, dispositivos como el RA4E2 y el RA6E2 brindarán una solución ideal. Estos dispositivos brindan soporte para opciones de paquetes pequeños como el BGA de 4 x 4 mm, al tiempo que admiten la interfaz I3C con un núcleo de rendimiento extremadamente alto, lo que los hace muy atractivos para estas nuevas aplicaciones de sensores.

Este artículo solo ofrece una mirada de alto nivel a la interfaz I3C. Los usuarios interesados pueden obtener más información sobre la interfaz MIPI Alliance I3C y descargar la especificación completa en el sitio web de MIPI en www.mipi.org/specifications/i3c-sensor-specification. Más información sobre los nuevos productos RA4E2 y RA6E2 está disponible en el sitio web de Renesas en www.renesas.com/ra.