Autor: Mark Patrick, Mouser Electronics

En la mayoría de diseños electrónicos, la sincronización es esencial para que todo funcione como se espera. Muchas aplicaciones requieren una combinación de señales de reloj síncronas en ubicaciones específicas de una PCI y de señales asíncronas en otras, algo que se conoce como distribución multirrama de señal de reloj. Cuando la sincronización se complica, el diseño de una distribución multirrama de señal de reloj también es más difícil. Una de las especificaciones más importantes en la sincronización es la fluctuación de fase y es una indicación de la variación en el periodo de una señal de reloj, Este índice empeora cuando el diseño de la distribución de señal de reloj es más complejo, así como en frecuencias altas. Esto significa que es muy difícil cumplir con las tolerancias, que suelen ser de femtosegundos (10-15) en aplicaciones de velocidad ultraalta. En este artículo, describiremos los principales componentes de una distribución de señal de reloj, veremos cuáles son los distintos tipos y orígenes de las fluctuaciones y hablaremos sobre lo que podemos hacer para reducir su impacto en los circuitos electrónicos.

Distribución multirrama de señal de reloj

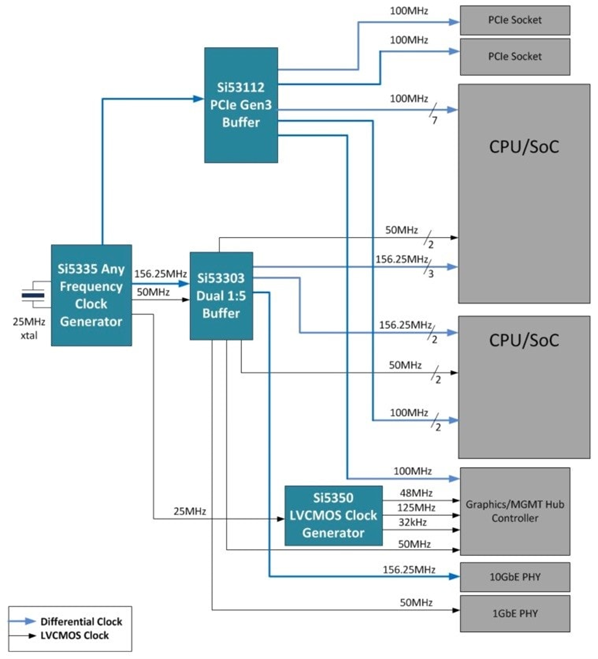

Los diseños de distribución de señal de reloj suelen estar personalizados para la aplicación, lo que significa que no hay una solución típica. En la imagen 1, se puede observar un ejemplo de distribución de señal de reloj con componentes de Silicon Labs.

Imagen 1: distribución de señal de reloj con varios relojes a partir de una combinación de monocristal y generador de reloj. (fuente: Silicon Labs)

Los circuitos de sincronización suelen consistir en uno o más de los siguientes elementos: un cristal de cuarzo, un oscilador de cristal, un búfer, un generador de reloj y un atenuador de fluctuaciones. Un cristal de cuarzo es un resonador piezoeléctrico que determina la frecuencia de la señal de sincronización. Se pueden fabricar para generar una frecuencia de señal precisa (32 kHz-50 MHz), que varía muy poco con la temperatura. Un oscilador de cristal (XO) es un circuito que usa la señal generada por el cristal de cuarzo para crear otras frecuencias de reloj necesarias en un formato asimétrico o diferencial. Un ejemplo de XO es el PL602-03 de Microchip, que puede funcionar con cristales de entre 12 y 25 MHz para generar una frecuencia de salida con poca fluctuación de 48 a 100 MHz. Un oscilador de cristal para controlar la tensión (VCXO) genera una frecuencia de reloj que se puede variar cambiando la tensión de entrada aplicada. El NB3N508S de ON Semiconductor es un VCXO que genera una salida de 216 MHz a partir de una señal de cristal de 27 MHz aplicando una tensión de entre 0 y 3,3 V en el pin VIN del dispositivo. Un generador de reloj es un CI que emplea la señal generada por un XO o un VCXO para producir muchas señales de reloj a diferentes frecuencias. El Si5338Q de Silicon Labs es un generador de reloj capaz de generar cuatro frecuencias de reloj independientes y programables por el usuario de hasta 350 MHz, así como otras frecuencias específicas hasta 710 MHz. Puede generar cuatro relojes diferenciales, ocho asimétricos u otras combinaciones.

Imagen 2: los generadores de reloj reducen el número de componentes en una placa. (fuente: Silicon Labs)

Un búfer de reloj, como el 9DBL0 de IDT, coge la señal de reloj del oscilador de cristal y la distribuye a diferentes lugares en la placa. Por otro lado, los atenuadores de fluctuación son componentes especializados que se usan para reducir (atenuar) la cantidad de fluctuación en señales de reloj en aplicaciones de alta velocidad, donde este fenómeno puede convertirse en un problema importante.

Qué es la fluctuación de fase

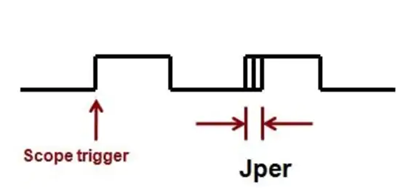

La fluctuación es una medida de la variación, en el periodo, de una señal de reloj en comparación con su valor ideal, y se mide en segundos. La fluctuación puede ser aleatoria o determinista. La fluctuación aleatoria está causada por los ruidos eléctricos que siempre generan los componentes electrónicos, pero suele ser pequeña y, normalmente, no afecta al funcionamiento del circuito. La fluctuación determinista suele ser repetitiva y se puede clasificar como periódica o dependiente de datos. Por ejemplo, la fluctuación causada por la conmutación en una fuente de alimentación es periódica porque coincide con la frecuencia de conmutación correspondiente. La fluctuación dependiente de datos puede ser periódica o aperiódica, y se crea por los cambios en los ciclos de trabajo y por cambios de estado irregulares en el reloj de una transmisión de datos en serie codificada en sistemas Ethernet o PCIe. Es difícil hacer un seguimiento de la fluctuación dependiente de datos, ya que depende del sistema. La fluctuación se suele clasificar de tres modos: absoluta, periódica y ciclo a ciclo. La fluctuación absoluta, conocida también como error de intervalo de tiempo (JTIE), es la diferencia de tiempo entre el momento en el que el reloj pasa del estado bajo al alto y su valor teórico calculado. La fluctuación periódica (Jper) es la diferencia entre el periodo de reloj más largo y más corto durante un determinado número de ciclos (imagen 3), y la fluctuación ciclo a ciclo (Jcc) es la diferencia máxima entre periodos de reloj consecutivos medidos durante un número determinado de ciclos.

Imagen 3: la fluctuación periódica es la diferencia entre el ciclo de reloj más largo y más corto durante una duración constatada. (fuente: Silicon Labs)

Efectos de la fluctuación

Una fluctuación excesiva puede afectar negativamente al rendimiento del circuito. En las aplicaciones de Ethernet síncrono (SyncE) y redes de transporte óptico (OTN), la JTIE causa pérdidas de sincronización, algo esencial para lograr un funcionamiento adecuado. La Jper y la Jcc son importantes en aplicaciones digitales porque tienen un impacto en la configuración y el tiempo de espera de cerrojos y «flip flops» y reducen el intervalo de muestreo de CAD de precisión, lo que limita la velocidad de un procesador digital. Es importante controlar de forma estricta la Jcc en aplicaciones que no pueden soportar los cambios en la frecuencia de reloj (imagen 4).

Imagen 4: una fluctuación excesiva provoca problemas de espera y muestreo, lo que genera que se pierdan o se corrompan datos. (fuente: IDT)

Cómo mejorar la fluctuación

La fluctuación se puede minimizar aplicando unos cuantos procedimientos recomendados en el diseño. Para empezar, es importante recordar que todo dispositivo electrónico introduce cierta fluctuación intrínseca en un circuito, así que tiene sentido intentar reducir el número de dispositivos siempre que sea posible. Los diseñadores también deberían procurar no especificar en exceso cuáles son los requisitos de fluctuación de un circuito, ya que la mayoría de ellos pueden funcionar adecuadamente aunque haya cierto nivel de fluctuación. A fin de reducir costes al diseñar la distribución de señal de reloj, podría parecer que una solución sería emplear menos cristales y generadores de reloj y más búferes de reloj, pero esto reduciría la precisión global de la sincronización en el sistema. La precisión de sincronización se puede mejorar aún más usando VCXO y búferes de retraso cero, pero eso aumenta la complejidad del diseño. Otras técnicas de diseño frecuentes para cumplir con los objetivos de sincronización son líneas de señales cortas (a fin de reducir la latencia de la distribución de señal de reloj), componentes adaptados detenidamente, longitudes de línea de reloj armonizadas o el empleo de separaciones y apantallamiento para evitar la diafonía de señales. Todo esto forma parte de procedimientos recomendados, pero no siempre garantiza una sincronización satisfactoria. Las IEM, las variaciones de tensión y el estrés mecánico (que afecta a las características piezoeléctricas del cristal) también contribuyen al nivel de fluctuación. Si la fluctuación de fase sigue siendo un problema, quizá sea necesario hacer un análisis detallado con instrumentación para determinar la causa principal del problema. La fluctuación se suele especificar en valores de media cuadrática (RMS) del incremento de tiempo (picosegundos o femtosegundos), ya que se presupone que tiene una distribución gaussiana. El resultado calculado es la desviación estándar de las mediciones de fluctuación, que se suelen llevar a cabo con un osciloscopio digital de alta velocidad. Estos instrumentos son particularmente útiles para medir la fluctuación dependiente de datos (JTIE, Jper y Jcc) con señales de reloj de alta o baja frecuencia. Tras recabar las mediciones sin procesar de la fluctuación, el valor RMS de la fluctuación se posprocesa. Luego, ese valor se convierte a un valor pico a pico con un cálculo de factor de cresta que asume una tasa de errores de bit aceptada (BER) de 10-12. Para este valor de BER, el factor de cresta es de 14,069, lo que significa que 1 ps de fluctuación RMS equivale a una fluctuación pico a pico de 14,069 ps.

Tras identificar la fluctuación problemática en la distribución de señal de reloj, se pueden usar algunas técnicas de diseño estándar para mejorar el problema. Esto incluye el uso de búferes multisalida (en lugar de varias instancias de un solo búfer) y escoger componentes de mejor rendimiento. También es conveniente rediseñar el trazado de las pistas o asegurarse de que tengan las mismas características físicas. En un sistema en el que la fluctuación aleatoria sea la principal causa de los problemas de sincronización, el método más lógico sería reducir el número de componentes al mínimo posible y sustituir cada componente con una pieza de mejores especificaciones hasta cumplir con el presupuesto. En situaciones excepcionales, quizá no sea posible cumplir con las especificaciones de fluctuación de un modo sencillo, incluso después de probar todo lo anterior. En esos casos, la única opción es emplear atenuadores de fluctuación en la distribución de señal de reloj, como el 8V19N407 de IDT o el Si5317 de Silicon Lab. Estos dispositivos filtran el ruido de la señal de reloj de entrada para producir una salida de reloj de fluctuación baja.

Conclusión

La fluctuación en señales de reloj es un causante principal de los problemas de sincronización en circuitos electrónicos, y tiene diferentes originadores. En este artículo, hemos analizado los tipos y orígenes de fluctuación en la distribución de señal de reloj, y hemos visto que podemos limitar su impacto combinando buenos métodos de diseño con una elección cuidadosa de los componentes.