Este artículo destaca los cambios introducidos en los siguientes estándares: IEEE 1149.1™-2013, revisión de IEEE 1149.6™-2003, IEEE P1149.10 e IEEE P1838

Las últimas revisiones y las nuevas propuestas para los estándares del IEEE abren nuevos horizontes a las pruebas de sistemas y placas de circuito impreso. Mientras la Ley de Moore sigue desafiando la existencia de los dispositivos electrónicos, la industria de la tecnología de prueba no se duerme en los laureles y se prepara para los retos que supondrá el avance en las necesidades de prueba de las tecnologías del futuro. Echemos un vistazo a las últimas novedades.

Estándar IEEE 1149.1™-2013 (revisión del estándar IEEE 1149.1-2001)

El estándar IEEE 1149.1, también conocido como rastreo periférico y JTAG (Joint Test Action Group) es una norma del IEEE (Institute of Electrical and Electronics Engineers) para probar puertos de acceso y arquitecturas de rastreo periférico. Sobre este estándar se basan los estándares IEEE 1149.4, 1149.6 y 1149.8.1.

Las revisiones del estándar IEEE 1149.1 contienen los siguientes cambios fundamentales:

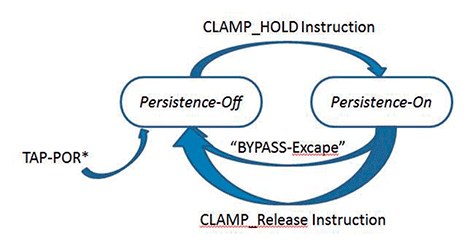

El controlador TMP constituye un modo de prueba en un dispositivo compatible montado en una placa de circuito o en un sistema durante las pruebas para que conserve su estado seguro cuando se esté aplicando la instrucción “Persistencia activada” del TMP. También impide que el dispositivo regrese a un modo funcional tras dispararse una instrucción de TLR (restablecimiento de lógica de prueba) u otra instrucción de modo no de prueba. La Figura 1 muestra un diagrama de máquina de estado del controlador TMP.

Estos modos de prueba han introducido tres nuevas instrucciones:

“CLAMP_HOLD”, “CLAMP_RELEASE” y “TMP_STATUS”. Las instrucciones “CLAMP_HOLD” ajustan el estado de TMP a “Persistencia activada”, mientras que las instrucciones “CLAMP_RELEASE” ajustarán el estado de TMP a “Persistencia desactivada”. “TMP_STATUS” lee el estado del controlador TMP.

Esta instrucción identifica cada dispositivo compatible leyendo la identificación por chip electrónico ECIDCODE única de cada matriz (“die”), que es como el número de serie de cada dispositivo.

Con su ayuda, el fabricante podrá identificar dispositivos falsificados o lotes con un rendimiento inferior durante las pruebas de placas, o incluso problemas de lotes debidos a un alto retorno de campo.

Estas instrucciones inicializan un dispositivo compatible para permitir la configuración de entradas/salidas (E/S) programables antes de llevar a cabo una prueba. Esto contribuirá al proceso de fabricación al lograr pruebas robustas y evitar daños internos en las placas que podrían producirse cuando los dispositivos bajo prueba no entran en un estado seguro.

Esta instrucción ofrece funciones de restablecimiento en un dispositivo compatible a través del puerto de acceso de pruebas (TAP). La instrucción IC_RESET permite controlar la función de restablecimiento del sistema del dispositivo durante pruebas de rastreo periférico.

Es un nuevo lenguaje para documentar los procedimientos de las nuevas instrucciones introducidas en esta versión del estándar IEEE 1149.1. PDL permite documentar las funciones internas del dispositivo, como la BIST (prueba automática integrada) de memoria, y su ejecución por parte de herramientas compatibles con el estándar. El estándar IEEE 1149.1™-2013, que puede descargarse en la página web del IEEE, ofrece procedimientos y muestras de PDL.

El estándar IEEE 1149.1™-2013 supone un gran avance desde el estándar IEEE 1149.1-2001. Las pruebas de rastreo periférico de placas de circuito impreso (PCBA) y de sistemas ahora abarcan BIST y otras pruebas que no se pudieron incluir en la revisión anterior.

IEEE 1149.6 (revisión del estándar IEEE 1149.6™-2003)

Con la publicación en 2013 del estándar IEEE 1149.1™-2013, hubo que actualizar el estándar IEEE 1149.6™-2003 para que las pruebas de rastreo periférico de redes digitales avanzadas pudieran adaptarse a los cambios introducidos en 1149.1.

En el momento de escribir este documento, el grupo de trabajo del estándar 1149.6 está preparándose para votar y se prevé que los cambios se publiquen este mismo año 2015.

El estándar IEEE 1149.6™-2003 se centra sobre todo en probar señales diferenciales de alta velocidad, que normalmente presentan un acoplamiento AC. Este tipo de señal suele distinguirse por un condensador de acoplamiento entre el emisor y el receptor (véase la Figura 2).

Antes de la formación del estándar IEEE 1149.6 a principios de la década de 2000, los sectores relacionados con las telecomunicaciones experimentaron una demanda cada vez mayor de velocidad, lo que fundamentó el aumento del uso de señales diferenciales de alta velocidad en componentes, lo que a su vez afectó a las pruebas de rastreo periférico de 1149.1, ya que este estándar se centraba principalmente en la interconexión de señales DC unipolares.

El estándar 1149.6 fue rápidamente adoptado por las empresas de telecomunicaciones, los fabricantes de componentes y los proveedores de equipos de pruebas automáticas (ATE).

El principal objetivo del grupo de trabajo de 1149.6 es incluir soporte del estándar IEEE 1149.1™-2013 para el proceso de inicialización durante las pruebas y la configuración de señales diferenciales de alta velocidad o controladores y receptores de prueba AIO (entradas/salidas avanzadas) que utilicen el PDL.

La historia nos muestra que la adopción de los estándares 1149.1 y 1149.6 aumentó sustancialmente cuando el sector de las telecomunicaciones empezó a demandar nuevos estándares a la medida de sus necesidades. Esta vez, no solo este sector, sino también industrias relacionadas con la informática, la información/entretenimiento y la computación móvil, demandan una mayor cobertura del rastreo periférico para incluir el acceso a instrumentos internos integrados y BIST durante las pruebas de placas o sistemas a medida que recuperan el alcance de prueba perdido a medida que se redujo el acceso de prueba a las placas de circuito impreso (PCBA).

Estándar IEEE 1687™-2014

El estándar IEEE 1687™-2014 también se conoce como JTAG de instrumentos (iJTAG). En este caso, el objetivo era desarrollar un método y normas para acceder a la instrumentación integrada en un dispositivo semiconductor sin necesidad de definir los instrumentos o sus características usando el estándar IEEE 1149.1. El estándar propuesto incluye un lenguaje descriptivo que especifica una interfaz que ayudará a la comunicación con la instrumentación integrada interna y las características del dispositivo semiconductor como BIST (prueba automática integrada), instrumentos integrados que normalmente solo están accesibles para los diseñadores de chips, así como otras funciones internas del dispositivo (véase la Figura 3).

El estándar IEEE 1687™-2014 o iJTAG permite utilizar el puerto de acceso de pruebas (TAP) IEEE 1149.1, presente en la mayoría de dispositivos, para gestionar la configuración, el funcionamiento y la recogida de datos desde los circuitos de instrumentación integrada dentro del dispositivo objeto. Los proveedores de equipos de prueba automatizados (ATE) también podrán acceder a los instrumentos integrados, BIST lógica e IP dentro del dispositivo para realizar pruebas de chips, placas o sistemas.

Los fabricantes electrónicos podrán volver a abarcar todas las pruebas con unos costes mínimos al incorporar esta solución en sus procesos de prueba actuales.

La adopción del estándar IEEE 1687™-2014 en las pruebas de flujos principales dependerá de cómo responda el sector. Cada segmento de actividad espera un dispositivo compatible con los estándares, y su adopción se basará en las necesidades del sector.

IEEE P1838

La propuesta de estándar IEEE P1838 se centra en la arquitectura de acceso de prueba para paquetes tridimensionales (3D) con múltiples matrices apiladas verticalmente con vías a través de silicio (TSV). La tecnología TSV permite apilar obleas y matrices de silicio con interconexiones verticales en cada capa de la oblea o matriz.

Véase a este respecto la Figura número 4.

En estos momentos, IEEE 1149.1 y 1149.6 son los dos estándares más adoptados en el sector de la fabricación, y admiten pruebas de interconexión de pines de un dispositivo compatible a los pines de otro dispositivo.

Los paquetes multinúcleo o multichip también se admiten siempre que cada matriz cuente con su lenguaje de descripción de rastreo periférico (BSDL) correspondiente, lo que permitirá al software ATE determinar la conexión entre dispositivos. No obstante, las conexiones internas dentro del paquete no forman parte de la lista del circuito impreso, por lo que no se probarán.

El otro reto es que cada matriz puede proceder de un proveedor distinto y, aunque se prueben individualmente y por separado al integrarse en un único paquete, las interconexiones entre las matrices no entran dentro del alcance de la prueba del estándar existente (véase la Figura 5).

Este vacío en el alcance de los paquetes multinúcleo o multimatriz será aún mayor una vez que el empaquetamiento 3D se extienda en el sector.

La propuesta IEEE P1838 ofrecerá a los proveedores un estándar común al que acogerse, permitiendo así que tanto las pruebas de placas como las de sistemas vuelvan a incluirse dentro del propio paquete 3D.